作者:877762833_166d01 | 来源:互联网 | 2023-09-01 16:59

ARM中所有寄存器都是32位的。这里以cortex-a7内核的MX6ULL处理器为例,按照功能可以分为两类:运行需要寄存器(程序正常运行所需要的,比如变量暂存,pc制作等,总共43

ARM中所有寄存器都是32位的。这里以cortex-a7内核的MX6ULL处理器为例,按照功能可以分为两类:运行需要寄存器(程序正常运行所需要的,比如变量暂存,pc制作等,总共43个),系统管理控制寄存器(存在于协处理器cp15的16个寄存器,用于mmu存储管理控制,cache控制,中断控制,浮点运算单元FPU等功能)。因此cortex-a7内核总的有59个寄存器。

1. 运行需要寄存器

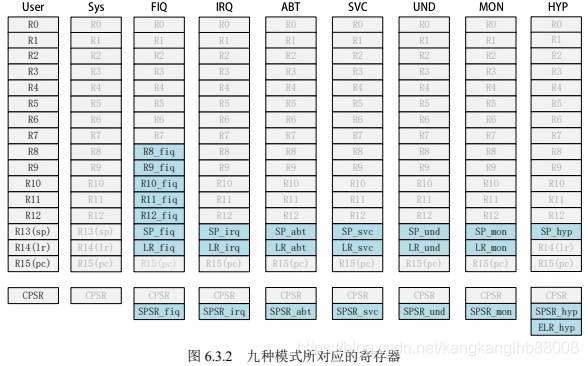

ARM 处理器共有 9种不同的处理器运行模式:

用户模式(User),快速中断模式(FIQ),普通外部中断模式(IRQ),超级管理模式(Svc,裸机就是跑的这个模式,cpu复位也是这个模式),数据访问中止模式(Abort),未定义指令中止模式(Und),系统模式(Sys),监视模式(Mon),超级监视模式(Hyp)

当某个触发满足了,arm自动进入那个模式,比如外部中断来了,arm自动跳转进入IRQ_Handler向量地址,这时候就是自动进入了IRQ模式(在下面介绍的CPSR状态寄存器对应的位可以查询知道当前所处模式,确实改变了)。

除了用户模式,其它所有模式都是特权模式,如果跑了OS,大多数的程序都运行在用户模式,用户模式下是不能访问系统所有资源的,而且不能修改某些资源(比如程序状态寄存器CPSR只能被访问,不能被修改,而该寄存器低5位表示CPU运行模式状态,因此用户模式没法直接发生运行模式切换,保障了系统安全,比如用户模式不能直接开关某某中断),有些资源是受限的,要想访问这些资源,就必须发生模式切换,只能是通过借助异常(比如SWI软中断,将进入SVC模式)来完成模式切换,当要切换模式的时候,应用程序可以产生异常,在异常的处理过程中完成处理器模式切换。

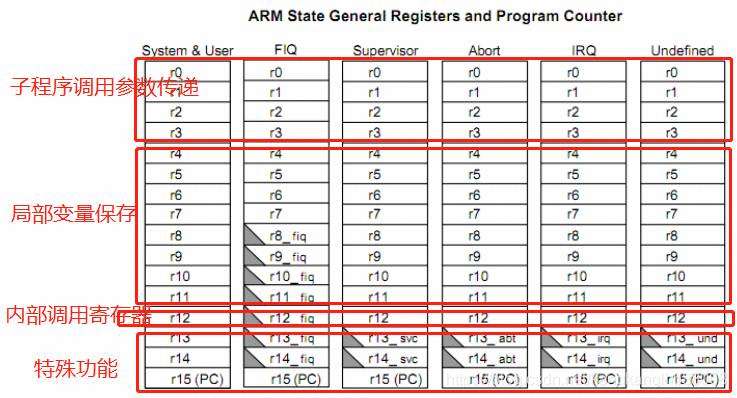

任意一种模式都可以运行程序,因此每种模式,按原则来说会有自己的一组寄存器来实现代码运行,但是有些寄存器是共用的,有些是仅自己用的(从物理上的寄存器不同)。如下图所示(只画出了7种运行模式):

上面可以看出系统模式,用户模式,都是正常模式,完全共用寄存器组,而其它模式都属于异常模式。

总结一下,CortexA 内核运行所需寄存器组成如下:

①、34 个通用寄存器,包括 R15 程序计数器(PC),这些寄存器都是 32 位的。

②、8 个状态寄存器,包括 CPSR 和 SPSR。

③、Hyp 模式下独有一个 ELR_Hyp 寄存器。

注:Thumb 程序中(arm指令集的一个子集,大大的节省了系统的存储空间,不是一个完整的体系结构,不能指望处理器只执行thumb指令集而不支持arm指令集),通常只能使用 r4~r7 来保存局部变量。

r12:内部程序调用暂存寄存器,也成为ip寄存器,我不知道是干嘛的,网上解释也模棱两可。

r13:栈指针,也称为sp寄存器

r14:连接寄存器,也称为lr寄存器,程序跳转(子程序调用,中断跳转)后,arm自动在该寄存器中存入原程序(未跳转)的下一条指令的地址。

r15:程序计数器,也称为pc寄存器,保存的是当前正在取指的指令的地址(arm采用2级流水线,因此是当前正在执行指令的地址+8)。

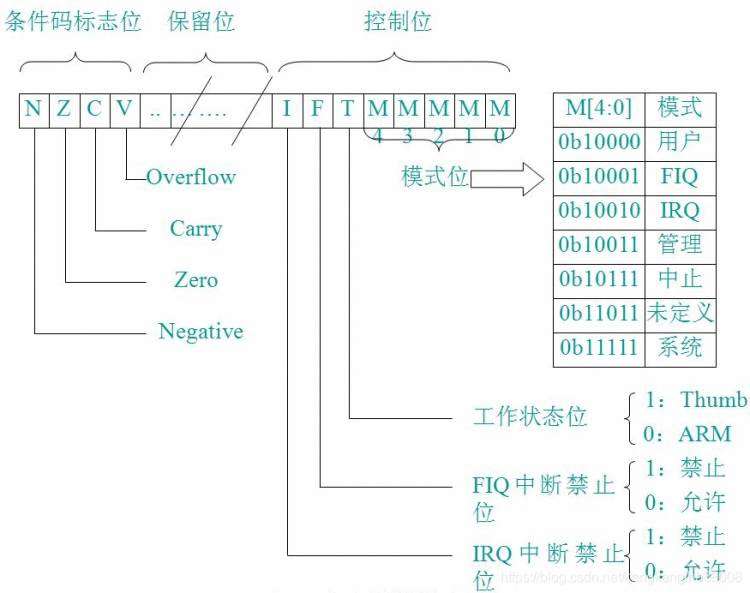

除了上述每种模式所需寄存器外,还有6状态寄存器,最主要的就是两个CPSR和SPSR,arm进入异常模式后,SPSR自动保存进入异常前的CPSR的值,以便异常返回后恢复异常发生时的工作状态。因此主要看CPSR中的位都是什么作用:

常用于MRS或MSR指令,用于spsr中的值转移到寄存器或把寄存器的内容加载到spsr中,如:

mrs r0, spsr /* 读取spsr寄存器 */

msr spsr_cxsf, r0 /* 恢复spsr */

2. 系统管理控制寄存器

关 于 CP15 协处理 器和其 相关寄存 器的详细 内容 请参考下 面两份文 档:《ARM

ArchitectureReference Manual ARMv7-A and ARMv7-R edition.pdf》第 1469 页“B3.17 Oranization of the CP15 registers in a VMSA implementation”。《Cortex-A7 Technical ReferenceManua.pdf》第55 页“Capter 4 System Control”。

CP15 协处理器一般用于存储系统管理,但是在中断中也会使用到,CP15 协处理器一共有

16 个 32 位寄存器。CP15 协处理器的访问通过如下另个指令完成:

MRC: 将 CP15 协处理器中的寄存器数据读到 ARM 寄存器中。

MCR: 将 ARM 寄存器的数据写入到 CP15 协处理器寄存器中。

MCR{cond} p15, ,

这个指令很难理解,还好的是所有控制寄存器,官方文档给出了库函数(通过c语言中嵌入汇编实现的),例如:

/* C语言实现MCR指令 */

#define __MCR(coproc, opcode_1, src, CRn, CRm, opcode_2) \

__ASM volatile (“MCR ” __STRINGIFY(p##coproc) “, ” __STRINGIFY(opcode_1) “, ” \

“%0, ” __STRINGIFY(c##CRn) “, ” __STRINGIFY(c##CRm) “, ” \

__STRINGIFY(opcode_2) \

: : “r” (src) )

/*******************************************************************************

* CP15 访问函数

******************************************************************************/

FORCEDINLINE __STATIC_INLINE uint32_t __get_SCTLR(void)

{

return __MRC(15, 0, 1, 0, 0);

}

FORCEDINLINE __STATIC_INLINE void __set_SCTLR(uint32_t sctlr)

{

__MCR(15, 0, sctlr, 1, 0, 0);

}

我学的是正点原子的MX6ULL教程,上述不知道是原子自己写的还是官方SDK里面都有的,在正点原子工程的imx6ul/core_ca7.h文件里,此外里面还有读取cpsr等寄存器的函数,非常方便。

其中比较重要的是,cp15的SCTLR寄存器

/* CP15的SCTLR寄存器

* 参考资料:Cortex-A7 Technical ReferenceManua.pdf P105

*/

typedef union

{

struct

{

uint32_t M:1; /*! uint32_t A:1; /*! uint32_t C:1; /*! uint32_t _reserved0:2; /*! uint32_t CP15BEN:1; /*! uint32_t _reserved1:1; /*! uint32_t B:1; /*! uint32_t _reserved2:2; /*! uint32_t SW:1; /*! uint32_t Z:1; /*! uint32_t I:1; /*! uint32_t V:1; /*! uint32_t RR:1; /*! uint32_t _reserved3:2; /*! uint32_t HA:1; /*! uint32_t _reserved4:1; /*! uint32_t WXN:1; /*! uint32_t UWXN:1; /*! uint32_t FI:1; /*! uint32_t U:1; /*! uint32_t _reserved5:1; /*! uint32_t VE:1; /*! uint32_t EE:1; /*! uint32_t _reserved6:1; /*! uint32_t NMFI:1; /*! uint32_t TRE:1; /*! uint32_t AFE:1; /*! uint32_t TE:1; /*! uint32_t _reserved7:1; /*! } b; /*! uint32_t w; /*!} SCTLR_Type;

还有FPU的3个相关寄存器:NSACR、CPACR、FPEXC寄存器