转载自:http://events.jianshu.io/p/1845b297f71d https://blog.csdn.net/m0_61896232/article/details/121095773

自动驾驶发展历程

自动驾驶行业发展现状:

感知层的视觉系统:舜宇、大立光、欧菲光;

毫米波雷达系统:大陆、博世、德赛西威、华域汽车;

激光雷达:ibeo、博世、velodyne、Quanergy、innoviz、雷神智能、禾赛科技、北科天绘、速腾聚创;

超声波雷达系统:电装、松下、村田;

数据服务商/地图厂家:百度、四维图新、高德;

决策层:mobileye、英伟达、安波福、东软、四维图新、中科创达; 芯片供应商:英伟达、英特尔、高通、华为、地平线;

车联网服务平台:联通智网、中移智行、九五智驾、四维智联;

执行层 控制方案整合:安波福、日本电装、博世;

单一类型传感器无法克服内生的缺点,我们需要将来自不同种类传感器的信息组合在一起,将多个传感器获取的数据、信息集中在一起综合分析以便更加准确可靠地描述外界环境,提高系统决策的正确性,比如典型的激光雷达+摄像头+IMU+高精度地图组合。

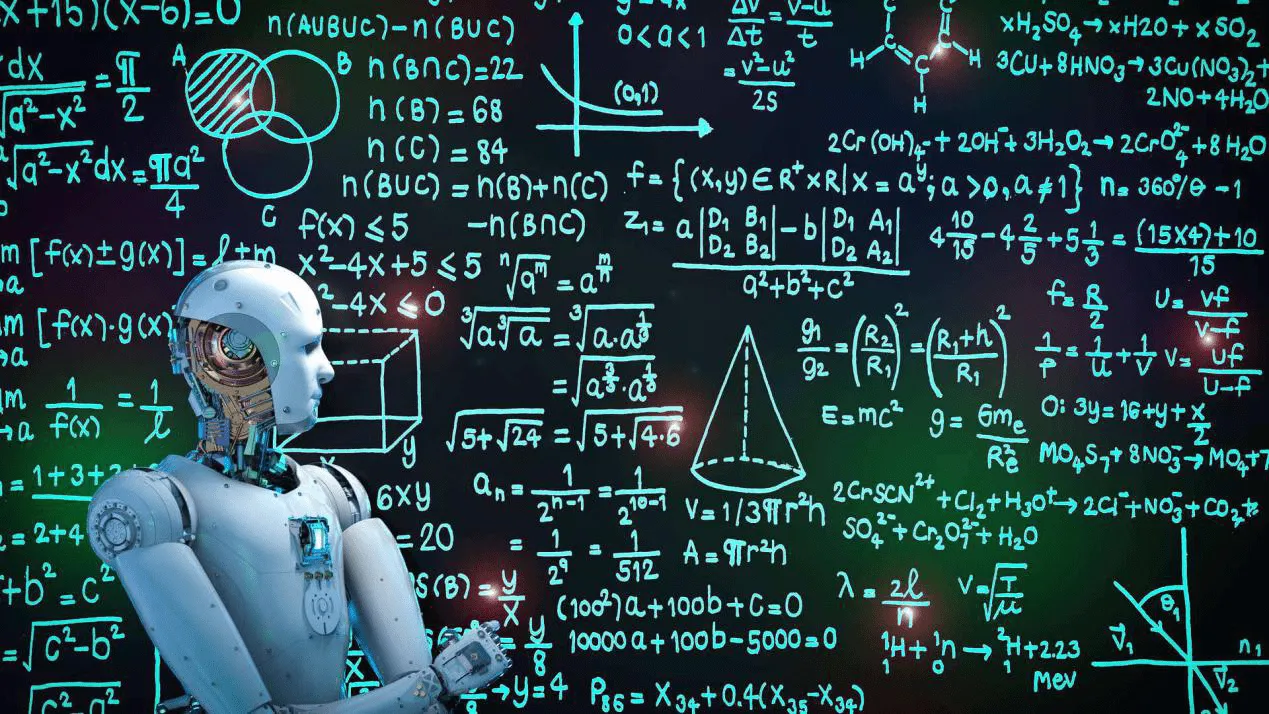

硬件架构升级驱动芯片算力需求呈现指数级提升趋势,汽车需要处理大量图片、视频等非结构化数据,同时处理器也需要整合雷达、视频等多路数据。这些都对车载处理器的并行计算效率提出更高要求,具备AI能力的主控芯片成为主流。

数据、算力和算法是AI三大要素,CPU配合加速芯片的模式成为典型的AI部署方案,CPU提供算力,加速芯片提升算力并助推算法的产生。常见的AI加速芯片包括GPU、FPGA、ASIC三类。

GPU是单指令、多数据处理,采用数量众多的计算单元和超长的流水线,主要处理图像领域的运算加速。但GPU无法单独工作,必须由CPU进行控制调用才能工作。CPU可单独作用,处理复杂的逻辑运算和不同的数据类型,但当需要大量的处理类型统一的数据时,则可调用GPU进行并行计算。

FPGA适用于多指令,单数据流的分析,与GPU相反,因此常用于预测阶段,如云端。FPGA是用硬件实现软件算法,因此在实现复杂算法方面有一定的难度,缺点是价格比较高。对比FPGA和GPU可以发现,一是缺少内存和控制所带来的存储和读取部分,速度更快。二是因为缺少读取的作用,所以功耗低,劣势是运算量并不是很大。结合CPU和GPU各自的优势,有一种解决方案就是异构。

ASIC是为实现特定要求而定制的专用AI芯片。除了不能扩展以外,在功耗、可靠性、体积方面都有优势,尤其在高性能、低功耗的移动端。

类脑芯片架构是一款模拟人脑的新型芯片编程架构,这一系统可以模拟人脑功能进行感知、行为和思考,简单来讲,就是复制人类大脑。

不同应用场景AI芯片性能需求和具体指标

AI芯片部署的位置有两种:云端和终端。云端AI应用主要用于数据中心,在深度学习的训练阶段需要极大的数据量和大运算量,因此训练环节在云端或者数据中心实现性价比最高,且终端单一芯片也无法独立完成大量的训练任务。终端AI芯片,即用于即手机、安防摄像头、汽车、智能家居设备、各种IoT设备等执行边缘计算的智能设备。端AI芯片的特点是体积小、耗电少,而且性能不需要特别强大,通常只需要支持一两种AI能力。

现阶段用于汽车决策控制芯片和汽车智能计算平台主要由三部分构成:

1)智能运算为主的 AI计算单元;

2)CPU单元;

3)控制单元。

主控SoC常由 CPU+GPU+DSP+NPU+各种外设接口、存储类型等电子元件组成,现阶段主要应用于座舱 IVI、域控制、ADAS等较复杂的领域。现有车载智能计算平台产品如奥迪 zFAS、特斯拉 FSD、英伟达Xavier 等硬件均主要由 AI(人工智能)单元、计算单元和控制单元三部分组成,每个单元完成各自所定位的功能。

特斯拉Model 3自研“中央-区EEA”架构:中央计算机是自动驾驶及娱乐控制模块(Autopilot & Infotainment Control Module),由两块FSD芯片承担大量的数据计算,主要服务于自动驾驶功能。两个区控制器分别是右车身控制器(BCM RH)和左车身控制器(BCM LH),主要服务于热管理、扭矩控制、灯光等功能。

FSD 的 HW3.0 由两个相同的计算单元构成,每个计算单元上面有特斯拉自研的2 块FSD计算芯片,每块算力位 36 Tops,设备总算力位 4 x 36 Tops = 144 Tops。但是由于采用的是双机冗余热备的运行方式,实际可用的算力为72 Top。

HW 3.0 PCB

LPDDR 全称是Low Power Double Data Rate SDRAM,是DDR SDRAM的一种,又称为 mDDR(Mobile DDR SDRM),是目前全球范围内移动设备上使用最广泛的“工作记忆”内存。特斯拉的LPDDR4(8BD77D9WCF)是Micron美光供应。FSD的GPS模块是NEO-M8L-01A-81,水平精度圆概率误差(英文简称CEP- CircularError Probable)为2.5米,有SBAS辅助下是1.5米,接收GPS/QZSS/GLONASS/北斗,CEP和RMS是GPS的定位准确度(俗称精度)单位,是误差概率单位。冷启动26秒,热启动1秒,辅助启动3秒。内置简易6轴IMU,刷新频率20Hz,量大的话价格会低于300元人民币。UFS(Universal Flash Storage)采用THGAF9G8L2LBAB7,Toshiba 2018年中期量产的新产品,车规级标准UFS,AEC-Q100 2级标准,容量32GB,由于特斯拉的算法模型占地不大倒也够用。MAX20025S是开关型电源稳压器,给内存供电的,来自Maxim Integrated,目前查不到更多的介绍资料。S512SD8H21应该是Boot启动,由Cypress(已被Infineon收购)供货。特斯拉用了3片TI的FPD-LINK,也就是解串器芯片,解串器芯片都是配对使用,加串行一般在摄像头内部,解串行在PCB上。两片DS90UB960,与其对应的可以是DS90UB953-Q1, DS90UB935-Q1,DS90UB933-Q1, DS90UB913A-Q1。DS90UB960拥有4条Lane,如果是MIPI CSI-2端口,每条Lane带宽可以从400Mbps到1.6Gbps之间设置。

上图为TI推荐的DS90UB960的典型应用示意图,即接4个200万像素帧率30Hz的YUV444数据,或者4个200万像素帧率60Hz的YUV420数据。DS90UB954是DS90UB960简化版,从4Lane减少到2Lane,与之搭配使用的是DS90UB953。由于大部分摄像头的LVDS格式只能用于近距离传输,因此摄像头都要配备一个解串行芯片,将并行数据转换为串行用同轴或STP传输,这样传输距离远且EMI电磁干扰更容易过车规。目前行业内做解串行芯片用的较多的就是德州仪器TI以及Maxim,特斯拉用的是德州仪器,而我们做开发接触的较多的是Maxim,可能是源于NVIDIA的AI芯片平台设计推荐,目前智能驾驶方面用的摄像头大部分都是Maxim方案。(摄像头的数据格式通常有RAWRGB、YUV两种。YUV常见的有三种级YUV444,YUV422和YUV420。计算带宽的公式是像素帧率比特*X,对RAW RGB来说X=4,比如一款摄像头输出30Hz,200万像素,那么带宽是200万x30x8x4,即1.92Gbps。YUV444是像素X帧率X比特X3,即1.44Gbps,YUV422是像素X帧率X比特X2,即0.96Gbps,YUV420是像素X帧率X比特X1.5,即0.72Gbps。ADAS通常对色彩考虑不多,YUV420足够。除车载外一般多采用YUV422。)

这款FSD芯片采用14nm工艺制造,包含一个中央处理器、1个图像处理单元、2个神经网络处理器,其中中央处理器和图像处理器都采用了第三方设计授权,以保证其性能和稳定性,并易于开发,关键的神经网络处理器设计是特斯拉自主研发, 是现阶段用于汽车自动驾驶领域最强大的芯片。

NPU的总功耗为7.5 W,约占FSD功耗预算的21%。这使得它们的性能功率效率约为4.9TOPs/W,特斯拉在芯片设计方面充分考虑了安全性,一块典型的自动驾驶电路板会集成两颗Tesla FSD芯片,执行双神经网络处理器冗余模式,两颗处理器相互独立,即便一个出现问题另一个也能照常执行,此外还设计了冗余的电源、重叠的摄像机视野部分、各种向后兼容的连接器和接口。

信号传输流程:从摄像头的图像开始,根据数据流向,特斯拉解释了整个过程。首先,数据以每秒25亿像素的最大速度采集输入,这大致相当于以每秒60帧的速度输入21块全高清1080P屏幕的数据。这比目前安装的传感器产生的数据多得多。这些数据然后进入我们前面讨论的DRAM,这是SoC的第一个也是主要瓶颈之一,因为这是处理速度最慢的组件。然后数据返回到芯片,并通过图像信号处理器ISP,每秒可以处理10亿像素(大约8个全高清1080P屏幕,每秒60帧)。这一阶段芯片将来自摄像头传感器的原始RGB数据转换成除了增强色调和消除噪音之外实际上有用的数据.

使用的是车载龙头镁光的LPDDR4,具体型号是8BD77D9WCF 8表示年份2018,B 表示第 4 周,D 代表 D-Die,属于镁光产品线中性能相对一般的型号,77 分别代表芯片生产地和封装地,7 代表中国台湾(5 代表中国大陆)。所以,这是一颗美光 2018 年第二周生产的D-Die颗粒)D9WCF对应型号为MT53D512M32D2DS-046AAT。53 代表这是一颗 LPDDR4 颗粒;D 代表1.1V 的工作电压;512M 表示单颗颗粒的容量为 512MB;32 表示单颗粒位宽为 32bit。

按照容量计算单颗芯片是=512MB X 32 ÷8 = 2GB,使用量是4颗,所以DDR的总容量是8GB。

按照LPDDR4最高频率4266MHZ的速率计算,每颗DDR是32位的位宽,CPU的位宽是32X4=128 bit,此时DDR的带宽=4266MBX128 ÷ 8 = 68.25G/S。

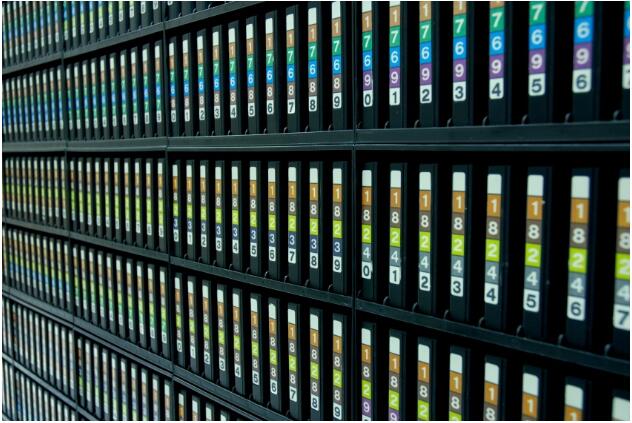

我们再来看看目前的特斯拉的信号传输流向。

可以看到,传输速度远远大于8颗摄像头采集的图像数据,传输速度不是瓶颈,ISP的处理速率是10亿像素/秒,如果是RGB888的位深,此时的数据量应该是2.78GB/S,此处的LPDDR4 的带宽是68GB/S,目前单独处理图像是够的。这里说内存带宽可能是未来限制自动驾驶的瓶颈,原因是要处理很多除了图像以外的数据,比如雷达,多线程多应用的数据。

自动驾驶对于DDR带宽的要求:

上图是目前比较主流的L3+自动驾驶的架构,从这里可以看到,摄像头那部分的处理需要的DDR的带宽是34GB/s,ASIC的DDR带宽为64bit,ADAS需要处理摄像头的raw dater,这样才是最原始的数据,不是压缩,也没有处理过的数据,这样ADAS处理起来才比较灵活,所以ADAS的带宽要求非常高。

可以看到除了要处理高清摄像头的raw dater的数据,还需要处理超声波雷达和激光雷达的数据,这些传感器的作用是不同的,激光雷达主要用于3D建模、超声波雷达用于倒车、超车,摄像头主要用于部分ADAS功能,比如ACC自适应巡航、AEB紧急制动等等。

自动驾驶传感器

上面FSD系统信号传输流程图 处理过程中,该过程的第一步是将数据存储在SRAM阵列中。现在很多人——甚至是那些对计算机组件略知一二的人——可能会想,“SRAM到底是什么?”嗯,最接近的比较是在计算机处理器上能找到的共享L3缓存。这意味着什么呢?这意味着存储速度非常快,但同时也很贵。

目前,Intel最大的L3缓存是45 MB(2010年以前是16 MB, 2014年以前是24 MB)。大多数消费级笔记本电脑和桌面处理器都有8-12 MB的L3缓存。特斯拉的神经网络处理器有一个庞大的64MB SRAM,它被分成两个32 MB的SRAM段来支持两个神经网络处理器。特斯拉认为其强大的SRAM容量是其相对于其他类型芯片的最大优势之一。

NPU的算力能够满足很多图像相关的识别算法:

假设此时你车上的AI图像算法是YOLO-V3,它是一种使用深度卷积神经网络学得的特征来检测对象的目标检测器,直白点就是照片识别器,在机场地铁都有批量使用,就是大量的卷积、残差网络、全连接等类型的计算,本质是乘法和加法。对于YOLO-V3来说,如果确定了具体的输入图形尺寸,那么总的乘法加法计算次数是确定的。比如一万亿次。(真实的情况比这个大得多的多),用算力表示就是TOPS为单位。那么要快速执行一次YOLO-V3,就必须执行完一万亿次的加法乘法次数。

人工智能(深度学习)现在无处不在,衡量人工智能运算量通常有三个名词。

人工智能中最消耗运算量的地方是卷积,就是乘和累加运算Multiply Accumulate,MAC。y = w[0]x[0] + w[1]x[1] + w[2]x[2] + … + w[n-1]x[n-1]w 和 x 都是向量,y 是标量。上式是全连接层或卷积层的典型运算。一次乘-加运算即一次乘法+一次加法运算,所以上式的 MACCs 是n。而换到 FLOPS 的情况,点积做了 2n-1 FLOPS,即 n-1 次加法和 n 次乘法。可以看到,MACCs 大约是 FLOPS 的一半。实际就是MAC只需一个指令,一个运算周期内就可完成乘和累加。卷积运算、点积运算、矩阵运算、数字滤波器运算、乃至多项式的求值运算都可以分解为数个 MAC 指令,人工智能运算也可以写成MAC运算。MAC指令的输入及输出的数据类型可以是整数、定点数或是浮点数。若处理浮点数时,会有两次的数值修约(Rounding),这在很多典型的DSP上很常见。若一条MAC指令在处理浮点数时只有一次的数值修约,则这种指令称为“融合乘加运算”/“积和熔加运算”(fused multiply-add, FMA)或“熔合乘法累积运算”(fused multiply–accumulate,FMAC)。假设3×3卷积,128 个 filer,输入的 feature map 是 112×112×64,stride=1,padding=same,MACCs 有:3×3×64×112×112×128=924,844,032次,即1.85TOPS算量。AI芯片就是简单暴力地堆砌MAC单元。增加MAC数量,这是提升算力最有效的方法,没有之一,而增加MAC数量意味着芯片裸晶面积即成本的大幅度增加,这也是为什么AI芯片要用到尽可能先进的半导体制造工艺,越先进的半导体制造工艺,就可拥有更高的晶体管密度,即同样面积下更多的MAC单元,衡量半导体制造工艺最主要的指标也就是晶体管密度而不是数字游戏的几纳米。具体来说,台积电初期7纳米工艺,每平方毫米是9630万个晶体管,后期7+纳米可以做到每平方毫米1.158亿个晶体管,三星7纳米是9530万个,落后台积电18%,而英特尔的10纳米工艺是1.0078亿个晶体管,领先三星,落后台积电。这也是台积电垄断AI芯片的原因。而5纳米工艺,台积电是1.713亿个晶体管,而英特尔的7纳米计划是2亿个晶体管,所以英特尔的7纳米芯片一直难产,难度比台积电5纳米还高。顺便说下,台积电平均每片晶圆价格近4000美元,三星是2500美元,中芯国际是1600美元。除了增加数量,还有提高MAC运行频率,但这意味着功耗大幅度增加,有可能造成芯片损坏或死机,一般不会有人这么做。除了简单的数量增加,再一条思路是提高MAC的效率。提高MAC效率方法:提升MAC效率最重要的就是存储。真实值和理论值差异极大。决定算力真实值最主要因素是内存( SRAM和DRAM)带宽,还有实际运行频率( 即供电电压或温度),还有算法的batch尺寸。例如谷歌第一代TPU,理论值为90TOPS算力,最差真实值只有1/9,也就是10TOPS算力,因为第一代内存带宽仅34GB/s。而第二代TPU下血本使用了HBM内存,带宽提升到600GB/s(单一芯片,TPU V2板内存总带宽2400GB/s)。最新的英伟达的A100使用40GB的2代HBM,带宽提升到1600GB/s,比V100提升大约73%。特斯拉是128 bit LPDDR4-4266 ,那么内存的带宽就是:2133MHz2DDR128bit/8/1000=68.256GB/s。比第一代TPU略好( 这些都是理论上的最大峰值带宽)其性能最差真实值估计是2/9。也就是大约8TOPS。16GB版本的Xavier内存峰值带宽是137GB/s。为什么会这样,这就牵涉到MAC计算效率问题,如果你的算法或者说CNN卷积需要的算力是1TOPS,而运算平台的算力是4TOPS,那么利用效率只有25%,运算单元大部分时候都在等待数据传送,特别是batch尺寸较小时候,这时候存储带宽不足会严重限制性能。但如果超出平台的运算能力,延迟会大幅度增加,存储瓶颈一样很要命。效率在90-95%情况下,存储瓶颈影响最小,但这并不意味着不影响了,影响依然存在。然而平台不会只运算一种算法,运算利用效率很难稳定在90-95%。这就是为何大部分人工智能算法公司都想定制或自制计算平台的主要原因,计算平台厂家也需要推出与之配套的算法,软硬一体,实难分开。最为有效的方法还是减小运算单元与存储器之间的物理距离。也是这15年来高性能芯片封装技术发展的主要目标,这不仅可以提高算力,还能降低功耗减少发热。这其中最有效的技术就是HBM和CoWoS。

CPU与HBM2之间通过Micro-bump连接,线宽仅为55微米,比传统的板上内存或者说off-chip内存要减少20倍的距离。可以大大缓解内存瓶颈问题。不过HBM和CoWoS价格都很高,假设500万的一次下单量,7纳米工艺的话,纯晶圆本身的硬件成本大约是每片芯片208-240美元,这个价格做训练用AI芯片可以承受,但是推理AI芯片用不起。再有CoWoS是台积电垄断的,台积电也正是靠这种工艺完全垄断高性能计算芯片代工。英特尔的EMIB是唯一能和CoWoS抗衡的工艺,但英特尔不代工。退而求其次的方法是优化指令集,尽量减少数据的访存,CNN算法会引入大量的访存行为,这个访存行为的频繁度会随着参考取样集合的增加而增加(原因很简单,缓存无法装下所有的参考取样,所以,即便这些参考取样会不断地被重复访问,也无法充分挖掘数据本地化所带来的cache收益)。针对这种应用类型,实际上存在成熟的优化范式——脉动阵列。脉动阵列脉动阵列并不是一个新鲜的词汇,在计算机体系架构里面已经存在很长时间。大家可以回忆下冯诺依曼架构,很多时候数据一定是存储在memory里面的,当要运算的时候需要从memory里面传输到Buffer或者Cache里面去。当我们使用computing的功能来运算的时候,往往computing消耗的时间并不是瓶颈,更多的瓶颈在于memory的存和取。所以脉动阵列的逻辑也很简单,既然memory读取一次需要消耗更多的时间,脉动阵列尽力在一次memory读取的过程中可以运行更多的计算,来平衡存储和计算之间的时间消耗。

下面说下脉冲阵列的基本原理:首先,图中上半部分是传统的计算系统的模型。一个处理单元(PE)从存储器(memory)读取数据,进行处理,然后再写回到存储器。这个系统的最大问题是:数据存取的速度往往大大低于数据处理的速度。因此,整个系统的处理能力(MOPS,每秒完成的操作)很大程度受限于访存的能力。这个问题也是多年来计算机体系结构研究的重要课题之一,可以说是推动处理器和存储器设计的一大动力。而脉动架构用了一个很简单的方法:让数据尽量在处理单元中多流动一会儿。正如上图的下半部分所描述的,第一个数据首先进入第一个PE,经过处理以后被传递到下一个PE,同时第二个数据进入第一个PE。以此类推,当第一个数据到达最后一个PE,它已经被处理了多次。所以,脉动架构实际上是多次重用了输入数据。因此,它可以在消耗较小的memory带宽的情况下实现较高的运算吞吐率。上面这张图非常直观的从一维数据流展示了脉动阵列的简单逻辑。当然,对于CNN等神经网络来说,很多时候是二维的矩阵。所以,脉动阵列从一维到二维也能够非常契合CNN的矩阵乘加的架构。降低推理的量化比特精度是最常见的方法。它既可以大大降低运算单元的精度,又可以减少存储容量需求和存储器的读写。但是,降低比特精度也意味着推断准确度的降低,这在一些应用中是无法接受的。由此,基本运算单元的设计趋势是支持可变比特精度,比如BitMAC 就能支持从 1 比特到 16 比特的权重精度。大部分AI推理芯片只支持INT8位和16位数据。除了降低精度以外,还可以结合一些数据结构转换来减少运算量,比如通过快速傅里叶变换(FFT)变换来减少矩阵运算中的乘法;还可以通过查表的方法来简化 MAC 的实现等。对于使用修正线性单元(ReLU)作为激活函数的神经网络,激活值为零的情况很多 ;而在对神经网络进行的剪枝操作后,权重值也会有很多为零。基于这样的稀疏性特征,一方面可以使用专门的硬件架构,比如 SCNN 加速器,提高 MAC 的使用效率,另一方面可以对权重和激活值数据进行压缩。

还可以从体系架构上对整个的Memory读取来做进一步的优化。这里摘取的是寒武纪展示的一些科研成果。其实比较主流的方式就是尽量做Data Reuse,减少片上Memory和片外Memory的信息读取次数,增加片上memory,因为片上数据读取会更快一点,这种方式也能够尽量降低Memory读取所消耗的时间,从而达到运算的加速。

对于神经网络来说,其实很多的连接并不是一定要存在的,也就是说我去掉一些连接,可能压缩后的网络精度相比压缩之前并没有太大的变化。基于这样的理念,很多剪枝的方案也被提了出来,也确实从压缩的角度带来了很大效果提升。需要特别提出的是,大家从图中可以看到,深度学习神经网络包括卷积层和全连接层两大块,剪枝对全连接层的压缩效率是最大的。下面柱状图的蓝色部分就是压缩之后的系数占比,从中可以看到剪枝对全连接层的压缩是最大的,而对卷积层的压缩效果相比全连接层则差了很多。所以这也是为什么,在语音的加速上很容易用到剪枝的一些方案,但是在机器视觉等需要大量卷积层的应用中剪枝效果并不理想。

对于整个Deep Learning网络来说,每个权重系数是不是一定要浮点的,定点是否就能满足?定点是不是一定要32位的?很多人提出8位甚至1位的定点系数也能达到很不错的效果,这样的话从系数压缩来看就会有非常大的效果。从下面三张人脸识别的红点和绿点的对比,就可以看到其实8位定点系数在很多情况下已经非常适用了,和32位定点系数相比并没有太大的变化。所以,从这个角度来说,权重系数的压缩也会带来网络模型的压缩,从而带来计算的加速。谷歌的TPU AI计算加速介绍:

这是Google的TPU。从上边的芯片框图可以看到,有一个64K的乘加MAC阵列对乘加运算进行加速。从论文中可以看到里面已经用到了脉动阵列的架构方法来对运算进行加速,另外也有我们前面提到的大量的片上Memory 这样的路径。上面蓝色框图中大家可以看到有一个24MiB的片上Memory,而且有两个高速DDR3接口能够与片外的DDR做交互。再来说说AI芯片。比如大名鼎鼎的谷歌的TPU1。TPU1,大约700M Hz,有256X256尺寸的脉动阵列,如下图所示。一共256X256=64K个乘加单元,每个单元一次可执行一个乘法和一个加法。那就是128K个操作。(乘法算一个,加法再算一个)。

另外,除了脉动阵列,还有其他模块,比如激活等,这些里面也有乘法、加法等。

所以,看看TPU1一秒钟的巅峰计算次数至少是=128K X 700MHz=89600Gops=大约90Tops。

对比一下CPU与TPU1,会发现计算能力有几个数量级的差距,这就是为啥说CPU慢。

当然,以上的数据都是完全最理想的理论值,实际情况,能够达到5%吧。因为,芯片上的存储不够大,所以数据会存储在DRAM中,从DRAM取数据很慢的,所以,乘法逻辑往往要等待。另外,AI算法有许多层网络组成,必须一层一层的算,所以,在切换层的时候,乘法逻辑又是休息的,所以,诸多因素造成了实际的芯片并不能达到利润的计算峰值,而且差距还极大。

上图展示的第二代TPU。从图中可以很直观的看到,它用到了我们前面所说到的HBM Memory。从其论文披露的信息也可以看到,二代TPU在第一代的基础上增加了我们前面说到的剪枝,权重压缩等方面做了很多尝试,也是一个非常经典的云端AI加速芯片的例子。

域控制其中最核心的是主芯片,一般会采用一颗或多颗高性能的SOC。SOC是System on Chip的缩写,就是在单块芯片上集成多个微处理器、模拟IP核、数字IP核和存储器等部件,比如CPU、GPU、DSP、ISP、Codec、NPU、Modem等模块。

这些单元,在一套总线系统的连接下,构成了一个系统。大家所熟知的各种手机SOC芯片,如苹果的A系列、高通的骁龙系列、华为的麒麟系列,或者各类的AI SOC芯片,车载领域的各种SOC芯片,都逃不出以上范式。虽然都是同一范式,但是由于使用的场景不同,各个芯片的侧重点不太一样:娱乐系统芯片,其实和消费电子几乎一模一样,关注音频、视频、显示、图像等、Modem等。自动驾驶芯片,注重高性能计算,一般配备有强大的NPU、GPU、DSP等。

优控智行的域控制器型号为EAXVA03,据说是第三代产品已经小批量装车。其内置NVIDIA Xavier和Infineon TC297T。按照设计部署,Xavier用于环境感知、图像融合、路径规划等,TC297用于安全监控、冗余控制、网关通讯及整车控制。综合以上各种因素,目前主流自动驾驶芯片的算力、功耗、算力功耗比、制程、SOP时间、芯片类型等相关信息对比如下:

可以看到,目前芯片基本上制程都往7nm和5nm开发,而且功耗越来越低,算力越来越高,即将上车的roin 单芯片算力达到200TOPS。

如上软件模块算法的算力效率牵涉到MAC计算效率问题。如果相应的自动驾驶模块算法或者说CNN卷积需要的算力是1TOPS,而运算平台的算力是4TOPS,那么利用效率只有25%,运算单元大部分时候都在等待数据传送,特别是批量待处理的尺寸较小时候,存储带宽不足会严重限制性能。但如果超出平台的运算能力,延迟会大幅度增加,存储瓶颈一样很要命。效率在90-95%情况下,存储瓶颈影响最小,但这并不意味着不影响了,影响依然存在。然而平台不会只运算一种算法,运算利用效率很难稳定在90-95%。

因此,是否能匹配比较高效的算法也是一个选择芯片平台的重要因素。

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有