作者:echo7111436 | 来源:互联网 | 2023-08-27 11:34

1.什么是EDMA3控制器?EDMA3(EnhancedDirectMemoryAccess3):增强型直接存储器访问的控制器。它是DSP中一个高效数据传输引擎,其结

1. 什么是EDMA3控制器?

EDMA3(Enhanced Direct Memory Access 3):增强型直接存储器访问的控制器。它是DSP中一个高效数据传输引擎,其结构适合数据的高速传输。直接存储器访问是一种重要的数据访问方式,可以在没有CPU参与的情况下,由控制器完成存储空间的数据转移,适用于软件触发的页面传输(片外存储空间与片内存储空间间进行传输)、适用于事件触发的外设(串口及接口UTOPIA)。利用EDMA3控制器对多变的数据结构进行子帧的提取及排列,减轻CPU在数据传输方面的负担。

2. EDMA3的特征

①提供三个维度完全正交的传输方式(三个维度之间不存在相互干扰);

EDMA3支持一维传输(A同步传输:一次触发只搬移ACNT个字节的数据)和二维传输(A-B同步传输:一次触发只搬运ACNT*BCNT个字节数据)这两种方式,不支持三维传输(A-B-C同步传输),但可以通过配置EDMA3为周期性事件触发模式,同时配置好CCNT的值,就可以实现A-B-C的三维传输。

②可变的独立源地址和目的地址;

EDMA3在初始化时会设定源地址和目的地址,在EDMA3的传输过程中,其源地址和目的地址会不断往后偏移,来实现数据从源地址+偏移位置往目的地址+偏移位置端转移。

③支持事件同步传输、手动同步传输以及链接同步传输方式;

事件同步传输:外设、系统或者外部产生的事件触发产生发送请求

手动同步传输:CPU通过在对应的寄存器位(ESR/ESRH)上写1来人为触发产生发送请求

链接同步传输:一个发送的完成来触发另一次的发送(要终止发送,可以将OPT中的LINK设为NULL)

④EDMA3具有64个DMA通道,8个QDMA通道,256个PaRAM参数集,每一个通道都可以与给定的事件队列和PaRAM相关联。

⑤EDMA3主要包括EDMA3CC(通道控制器)和EDMA3TC(传输控制器),EDMA3CC是用户控制EDMA控制器的接口,是EDMA3中用户编程的一部分。EDMA3CC包括PaRAM参数、通道控制寄存器以及中断控制寄存器。传输控制器EDMA3TC负责数据的搬移并分别向源地址和目的地址发出读写命令,源地址和目的地址是在EDMA3CC中设定的。

3. EDMA3CC主要以下几个模块

1. PaRAM:PaRAM参数设置了数据传输的一些信息,例如源地址、目的地址、传输的数据大小,以及传输方式等信息。

2. EDMA3事件和中断处理寄存器:实现事件和参数设置的映射,事件使能/去使能,中断使能/去使能/清除中断等。

3. 事件队列:事件队列处于事件探测逻辑和发送请求提交逻辑之间。

4. 内存保护寄存器:内存保护寄存器定义了DMA通道阴影区域和PaRAM区域的入口。

5. 区域寄存器:区域寄存器允许DMA源(DMA通道和中断)被分配到独特的区域。

6. 调试寄存器:调试寄存器允许访问可视的寄存器来读取队列状态、控制器状态和事件状态。

4. PaRAM参数集

EDMA3共有256个PaRAM参数集,DMA和QDMA的通道传输内容(源/目的地址、数量、索引值等)都是在PaRAM中设置的。用户可以将256个PaRAM映射到任意DMA通道或QDMA通道上,来控制传输控制器进行一定数据量的搬运。

PaRAM各字段含义

| 字段 | 含义 |

| OPT | 传输配置选项 |

| SRC | 数据来源端的字节地址 |

| ACNT | 一个array中的连续字节数 |

| BCNT | 一帧中的array数 |

| DST | 数据目的端的字节地址 |

| SRCBIDX | 源BCNT索引值,用于指示传输帧中, 数据源的阵列array的间隔 |

| DSTBIDX | 目的BCNT索引值,用于指示传输帧中, 数据目的端的阵列array的间隔 |

| LINK | 当前PaRAM耗尽时,用于LINK的PaRAM的地址 |

| BCNTRLD | A同步传输时,BCNT耗尽时的重载值 |

| SRCCIDX | 源CCNT索引值,用于指示传输帧中, 数据源的帧间的间隔 |

| DSTCIDX | 目的CCNT索引值,用于指示传输帧中, 数据目的端的帧间的间隔 |

| CCNT | 一个传输块中的帧数 |

5. DMA与QDMA的区别

DMA和QDMA通道的不同之处在于使用的触发条件不同。DMA的触发方式有三种:主动触发、事件触发以及链接触发。而QDMA的触发方式是自动触发和链接触发模式,自动触发是指只要配置了PaRAM参数就会自动触发,链接触发与DMA比较类似。QDMA只能发送一维Array的数据格式,而DMA可以发送一维、二维和三维的数据格式。

4. 配置EDMA3发送的主要步骤

1. DMA通道的初始化:

a. 通道选择,包括通道类型选择以及通道号选择,特别是事件触发时,不同的事件绑定了不同的通道号(在主动触发方式下,可以任意选择通道号,但如果是事件触发模式,必须使用触发事件对应的通道号)。

#define g_Edma3ChanNUM 20

#define g_PaRAMNum 30

/*EDMA3有64个DMA通道,8个QDMA通道,可任意选择通道号,但主要不要冲突*/

/*PaRAM共有256个参数集,可任意映射至DMA通道和QDMA通道,注意不要冲突*/

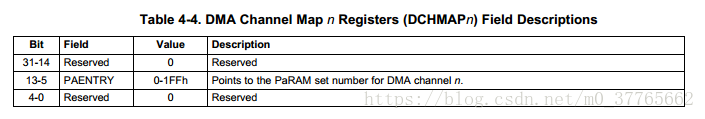

b. 通道映射,配置DCHMAP寄存器,指定PaRAM参数地址映射到使用的通道号

*(Edma3_DCHMAP0 + 4 * g_Edma3ChanNUM) = g_PaRAMNum <<5;

/*将PaRAM 30 映射到DMA通道20 上*/

※ 此处寄存器中显示可以配置0-511个PaRAM,但实际上只有256个PaRAM

c. EDMA通道分区设置,EDMA3通道控制器寄存器分为全局寄存器、全局区域寄存器和阴影区域寄存器,如果将某个通道设置为阴影区域,那么后续操作必须使用阴影区域的寄存器(一般不用阴影区域,可以不用配置)。

d. 阴影区域通道使能,打开相应的DMA通道中断使能;

/*如果使用的通道为阴影区域,则需要置位对应阴影通道的使能寄存器*/

e. 将选择的EDMA通道设置到需要的队列上,每个队列的优先级是不同的。

*Edma3_DMAQNUM0 = 0x44444444;

/*将选择的通道设置到队列4上,EDMA3CC共有8个队列,每个队列深度是16个事件,也就是说一个队列可以配置16个通道的队列号*/

2. PaRAM参数配置

根据搬移的数据类型,参照PaRAM各字段含义,将PaRAM的参数写入与使用通道绑定的PaRAM中。

*t_PARAM_ADDR ++ = 0x0010000C; //写入OPT

*t_PARAM_ADDR++ = (UINT)0x00801000; //写入SRC

*t_PARAM_ADDR++ = (16<<16) + 16; //写入BCNT ACNT

*t_PARAM_ADDR++ = (UINT)0x00802000; //写入DST

*t_PARAM_ADDR++ = (16<<16) + 16; //写入STBIDX SRCBIDX

*t_PARAM_ADDR++ = 0x0001FFFF; //写入BCNTRLD LINK

*t_PARAM_ADDR++ = 0x0000000; //写入DSTCIDX SRCCIDX

*t_PARAM_ADDR++ = 0x00000001; //写入Rsvd CCNT

3. 中断配置

PaRAM中的OPT字段中应该使能相应的中断,另外需要通过设置IESR/IESRH使能中断相应。

4. 触发传输

a. 事件触发,通道如果触发源是事件,即当外部事件发生时,EDMA3自动传输一次数据。

b. 手动传输,通过CPU手动配置ESR寄存器触发

*Edma3_ESR = 0x1<//触发传输

c. 链接触发,当上一个通道的传输完成码等于下一DMA通道时,上一通道传输完成将触发下一通道传输数据。

5. 等待完成

a. 在中断复位函数中等待,如果按照3中的设置,那么当传输完成后,EDMA3会给CPU产生中断,中断函数中必须将IPR/IPRH清零,方便下次实用性相同的标志位。

b. 轮询寄存器,如果未使能中断相应,那么可以等待相应的IPR/IPRH位置1,表示传输完成,IPR/IPRH必须清零,方便下次使用相同的标志位。

附表:EDMA3通道同步事件对照表

EDMA3 Channel Synchronization Events

| Channel | Event | 30 | TCP2_A Receive Event |

| 0 | HPI/PCI-to-DSP Event | 31 | TCP2_A Transmit Event |

| 1 | Timer 0 Lower Counter Event | 32 | UTOPIA Receive Event |

| 2 | Timer 0 Higher Counter Event | 33 | TCP2_B Receive Event |

| 3-8 | None | 34 | TCP2_B Transmit Event |

| 9 | Embedded Trace Buffer (ETB) is Half Full | 35-39 | None |

| 10 | Embedded Trace Buffer (ETB) is Full | 40 | UTOPIA Transmit Event |

| 11 | Embedded Trace Buffer (ETB) Acquisition is Complete | 41-43 | None |

| 12 | MCBSP0 Transmit Event | 44 | I2C Receive Event |

| 13 | MCBSP0 Receive Event | 45 | I2C Transmit Event |

| 14 | MCBSP1 Transmit Event | 46-47 | None |

| 15 | MCBSP1 Receive Event | 48 | GPIO Event 0 |

| 16 | Timer1 Lower Counter Event | 49 | GPIO Event 1 |

| 17 | Timer1 Higher Counter Event | 50 | GPIO Event 2 |

| 18 | None | 51 | GPIO Event 3 |

| 19 | RapidIO Interrupt 0 | 52 | GPIO Event 4 |

| 20 | RapidIO Interrupt 1 | 53 | GPIO Event 5 |

| 21 | RapidIO Interrupt 2 | 54 | GPIO Event 6 |

| 22 | RapidIO Interrupt 3 | 55 | GPIO Event 7 |

| 23 | RapidIO Interrupt 4 | 56 | GPIO Event 8 |

| 24 | RapidIO Interrupt 5 | 57 | GPIO Event 9 |

| 25 | RapidIO Interrupt 6 | 58 | GPIO Event 10 |

| 26-27 | None | 59 | GPIO Event 11 |

| 28 | VCP2 Receive Event | 60 | GPIO Event 12 |

| 29 | VCP2 Transmit Event | 61 | GPIO Event 13 |

| 30 | TCP2_A Receive Event | 62 | GPIO Event 14 |

| 31 | TCP2_A Transmit Event | 63 | GPIO Event 15 |