单板级SSN

从单板级来看,芯片中多个逻辑门同时翻转时,将从单板电源和地平面瞬间汲取较大的电流。任何电源分配系统都存在着阻抗,特别是感抗,导致在短时间内电压调整模块来不及供应这些电流,从而在单板和电源之间出现感应噪声,波及整个电源分配系统。

减小SSN的影响

SSN这种现象的起因很多,有时候表现得令人难以捉摸,不过可以通过其产生的原理来减小它的影响。由于V=L*(dI/dt),要减小前者,就需要减缓电流的瞬间变化幅度(dI/dt),同时减小电流流过路径的电感L。

在设计FPGA时,要减小芯片级SSN,首先可以考虑如何减小硅片到PCB地的连接电感L。

1、 用剩余的IO做可编程VCC/GND,增加电源和地的连接点,可以有效的减小电感。建议把可编程VCC和GND放在同步翻转输出(SSO)管脚的附近。

2、 把同步翻转输出(SSO)尽量散布开。由于在FPGA中,一对电源地线通常支持部分IO,可以把SSO管脚尽量分散开,最好是分布到不同的IO bank中。

3、 把SSO尽量靠近VCC/GND对同样可以有效的减小电流回路电感。

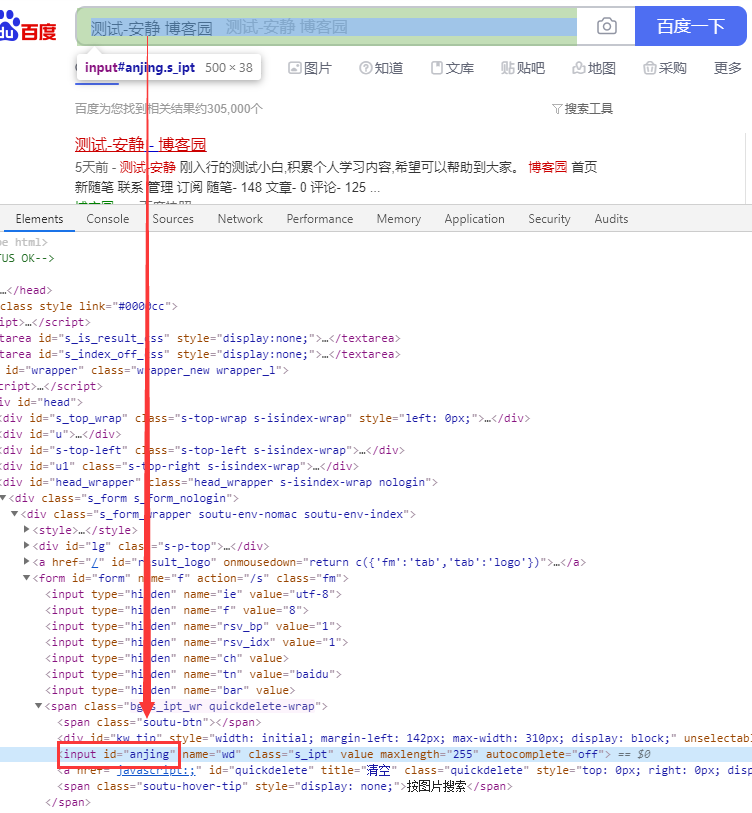

4、 在器件选择时,尽量考虑Flip-chip(倒装)的封装。它比wire-bond(打金线)的器件具有更短的连线,而且有更好的参考面和更小的感抗值,如下图,左边为wire-bond,右边为flip-chip。也可以通过减小dI/dt来减小SSN。

wire_bond 和flip-chip的封装

5、 在FPGA内部的一些IO标准中,用户可以自己设置输出的电流强度。把输出的电流设置的越小,dI/dt也就越小,但同时会降低IO性能。

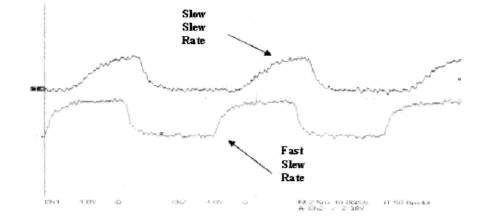

6、 用户可以把翻转率(slewrate)设置为慢速(slow)方式,这样可以显著减小dV/dt,因此也可以减小dI/dt,如下图:

快速和慢速翻转速率波形效果

7、 减小SSO的数量是最直接的减小SSN的方法。

8、 用户可以通过一些方法,使得SSO在不同的时间翻转来减小同一时间所消耗的电流。例如用户可以利用PLL分出相位略有差异的不同的时钟域,分别驱动部分SSO。当然,这样做需要在保证系统时序的前提之下。

9、 如果用户使用 加源端串阻的IO标准,使得输出电流或信号输出幅度减小,同样可以达到减小dI/dt的目的。

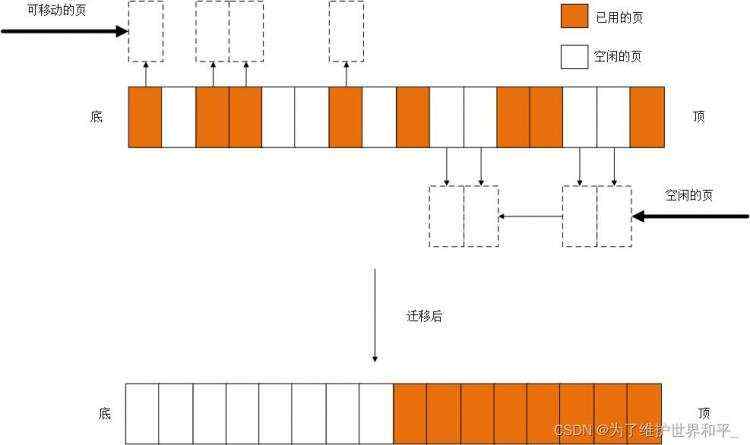

如果需要减小SSN在PCB上的影响,用户需要在SSN的起源处加去耦电容,也就是在VCC/GND管脚处加容值较小的去耦电容。它相当于一个临时的蓄水池,将满足SSO需要的瞬态电流。

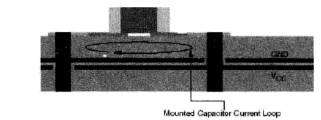

在PCB上加去耦电容需要注意把电容尽量放置在靠近VCC/GND对的地方,同时电容的PCB引线尽量短,以减小电流环路的面积,也就是减小环路阻抗,如下图:

去耦电容形成的电流环路

在单板上增加去耦电容,也是为了使电源系统对同步翻转噪声呈现低阻抗,这样SSN就不会给电源系统带来较大的波动,这也是电源分配系统的设计者所追求的目标。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

京公网安备 11010802041100号

京公网安备 11010802041100号