origin: http://www.sitchip.com/?page_id=706

Synplicity的HAPS系列产品是专为ASIC/SOC设计者提供的高性能、高容量的基于FPGA的原型验证板。HAPS是由母板和子板组成的系统,母板上配置了一片或多片高性能的FPGA芯片,不同的母板可以进行叠加,以适应大容量ASIC/SOC的验证需要。子板可以根据需要从Synplicity提供的几十种标准库中选择,也可以自己定制。

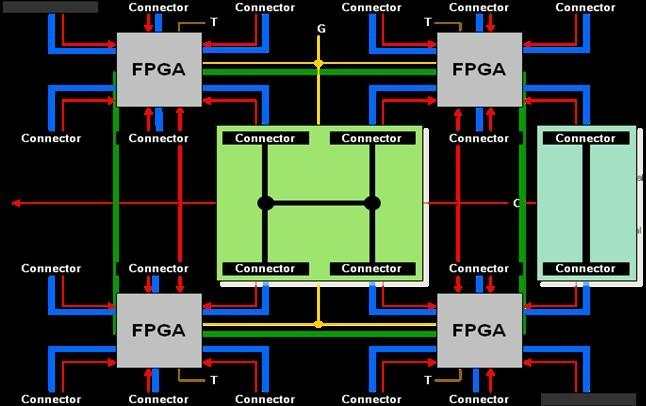

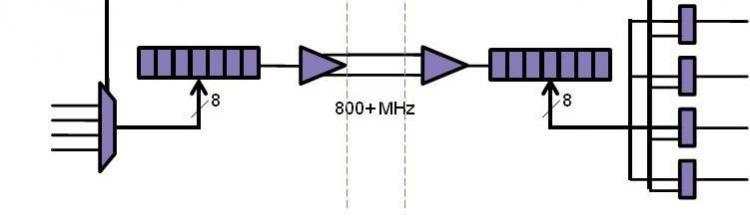

HAPS母板是验证系统的主体部分,母板上的高容量FPGA用于例化待验证的ASIC设计,在每个FPGA的四周均匀排列着6个HapsTrack连接头,为提高验证系统的性能,减少信号的扭曲,从FPGA到每个HapsTrack连接头的走线采用蛇形线的方法(见图1),以达到长度相等,这些走线的长度误差在5 皮秒以内。

HAPS母板上的FPGA之间的 连接线可动态配置。除了板上固定数量的连接线以外,HAPS母板可以根据项目的实际需要,灵活配置FPGA间的连接线。

借助于标准库中的连接板,FPGA间的连接线可成倍的增加。这个特性对于满足不同项目中不同数目的连接线的要求,从而僻免重新制版,降低成本,缩短开发周期,有着重要的作用。

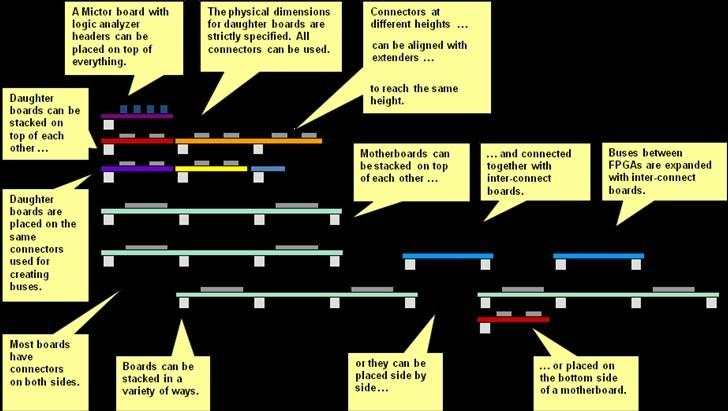

HAPS母板具有可重用性。不同的验证项目要求不同的FPGA的容量、FPGA间的连线以及不同的接口配置。HAPS的理念可以很好的满足之一要求。各个FPGA周围的HapsTrack连接头在电器特性和物理特性上统一定义,这样可以使不同容量和接口的验证系统达到无缝连接的要求,他同时可以杜绝开发系统的浪费,从而降低系统开发的成本。图3是利用不同时期购买的HAPS母板组成一套新的大容量的验证系统的方案。

HAPS子板是验证系统的对外接口,子板与母板一起,组成完整的验证系统。标准库中提供各种通用的子板,其中memory包括: SRAM,SDRAM,DDR,DDR2,GDDR,FLASH,视频子板包括视频编解码板AVID,HDMI接口板DVI,USB接口板ETH_USB,以太网接口板GEPHY,PCIE接口板PCIE-4-Kit,PCI接口板PCIX,模数转换板ADC,MPEG接口板DVB-OUT,液晶接口板LCD,ARM Core Tile转接板HAPS_CMI,连接线板CON_2x1,CON_1x2,CON_2x2,CON_1x1,CON_Cable40等。

由于HAPS方案具有的高鲁棒性以及高可靠性,它可以实现很高的设计性能,可以使ASIC/SOC设计者更加集中精力在ASIC设计本身,从而为芯片的设计开发节约多达数月的时间。HAPS单板是通用的系统验证板,可以在不同的项目开发中重复使用。并且可以用于在ASIC芯片量产前的客户演示,ASIC/SOC芯片的早期功能测试,早期的软件开发,软硬件协同测试等。由于HAPS原型验证板的诸多优势,已经被业界很多著名厂商使用,比如:Broadcom, Conexant, LG, LSI Logic, Marvell, Matsushita ,Nokia, NXP, Philips, Samsung, Sharp, Sony, TI,等。

通过40层的PCB布线实现单板高速信号完整性的要求和高性能的要求

4 片Virtex-6 LX760 (1760管脚封装)

每块母板可实现相当于18 百万 ASIC Gates容量

可以满足高速系统速度的要求(100-200 MHz)

可以提供多达3663个I/O 和FPGA 互联线

全局总线,可以方便的实现与其它母板的互联

13个全局,高速度、低Skew时钟信号

265个局域时钟 – LVDS or Single-ended模式

支持Differential时钟模式

多达15 个VCCO电平区域 (, 2.5, 1.8, 1.5, 1.2 V)

多种FPGA配置方式:通过Cable 或CompactFlash Card,或者通过板SelectMAP配置;

可以实现FPGA温度自动调节的风扇

FPGA管脚短路和断路自动检测

仅需要12V电压供电即可;

UMRBUS总线支持高级验证功能以及远程配置控制.

优势:

1) 高性能

a) 从FPGA到每个connector有119根有效I/O信号,这组信号线是等长的, 误差在5ps以内, 相等的长度可以克服信号传输路径不同带来的timing 延时的不等,提高设计的性能;

b) 13个时钟输入接口到板上4个FPGA的走线等长,这可以最大限度的减少时钟的Skew,保持个FPGA时钟的同相, 从而提高设计的稳定性;

c) PCB板材采用独特的高速PCB材料, 以提高系统的性能;

d) FPGA对外的信号连接器采用特殊的低噪声连接器,可以增强信号的鲁棒性;

e) 板子设计支持数控阻抗技术, 以动态适应外界温度/压力等环境的改变, 增强系统的稳定性.

2) 板上动态内连技术

a) HAPS板支持FPGA间连线的动态配置. FPGA间有丰富的固定的互联线, 与不同的项目配合, FPGA间的互联线可以通过连接板动态的增加或减少;

b) 当需要大数目的FPGA间的互联线时(超过500), 可以与Synopsys的分割工具Certify配合,自动的利用Synopsys独有的HSTDM技术,动态的增加FPGA间的互联线.

3): 支持高级验证功能

HAPS-60系列中有一组UMRBUS总线, 这组总线通过PCIE和主机相连, 在主机和HAPS-60间建立通信关系. 基于这组总线, 一些高级的验证功能可以在HAPS上实现

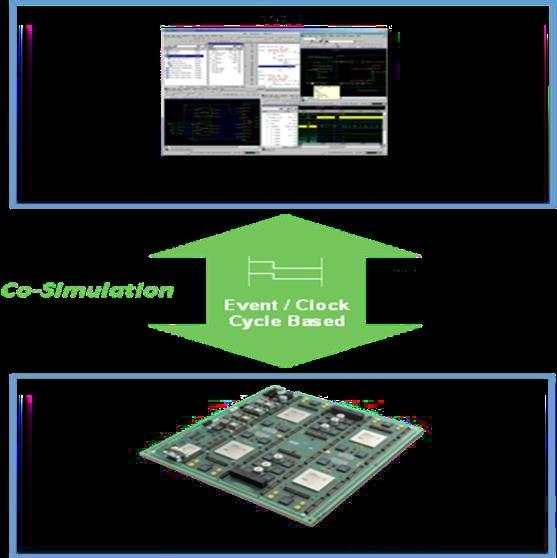

a) Co-simulation.

在这种方式,基于Verilog或VHDL的Testbench运行在主机上的VCS中, 而待测模块(DUT)运行在FPGA中, 减轻了主机的负担, 可以使仿真速度加快几十倍到上百倍.

b) SCEMI2.0 co-emulator

在这种方式,基于C/C++, Synyem C, SystemVerilog的Testbench运行在主机上, 而待测模块(DUT)运行在FPGA中. 由于是基于事务级的协同仿真, 其仿真速度可以提升成千上万倍.

4): 自检测功能

在HAPS中,内嵌自检测程序, 可以完成对板子的保护和诊断:

a): 自动电压/温度检测:

HAPS系统自动检测板子的温度, 进而控制风扇的运行, 这样可以是板子运行在一个稳定的环境; 板上的各种电压都可以读出, 从而更好的维护硬件环境.

b): 自动开路/短路检测:

HAPS带开路/短路检测电路, 这样可以界定调试过程中硬件和软件bug,从而加速验证的进程.