浅析quartus2中的几种技术视图 标签: qaurtus2 technology viewer

今天浅析一下软件中的几种视图,平时也许我们对他们的关注度不大,但是在实际中他们却是很有用的。

一、Timing closure floorplan(时序收敛平面)

如图1所示,在该图中可以看到以下内容:一、可以看到程序综合布线后在FPGA中实际占的位置 二、可以选择查看各个节点的扇入扇出,以及该节点与其他的延时,可以作为时序收敛调整的依据 三、可以设置关键的路径的建立,保持时间参数(后面详解) 四、可以在该平面设置逻辑锁区域,还可以反标注逻辑锁区域(后面详解)

二、RTL viewer(寄存器传输级视图)

这是程序在早期综合后,未经优化,我们看到的在寄存器级别的对程序的表达,你可以通过查看该视图,来看有没有综合出你想要的元件,如你想在输出口有一个寄存器,你想让输出口是一个三态口,你在程序中设计了一个计数器,还可以通过查看该图来修改程序,实现资源优化。

如图2所示,你可以看到,图中显示分为三大类,instances(即为你在程序中实例化的各个模块),pins(即为整个工程的输入输出口)nets(即为各个模块之间,模块与输入,输出之间的连线网络)。注意最开始看到的是整体模块图,你可以双击每个模块进入低一层,直到看到最后的寄存器级网表的。

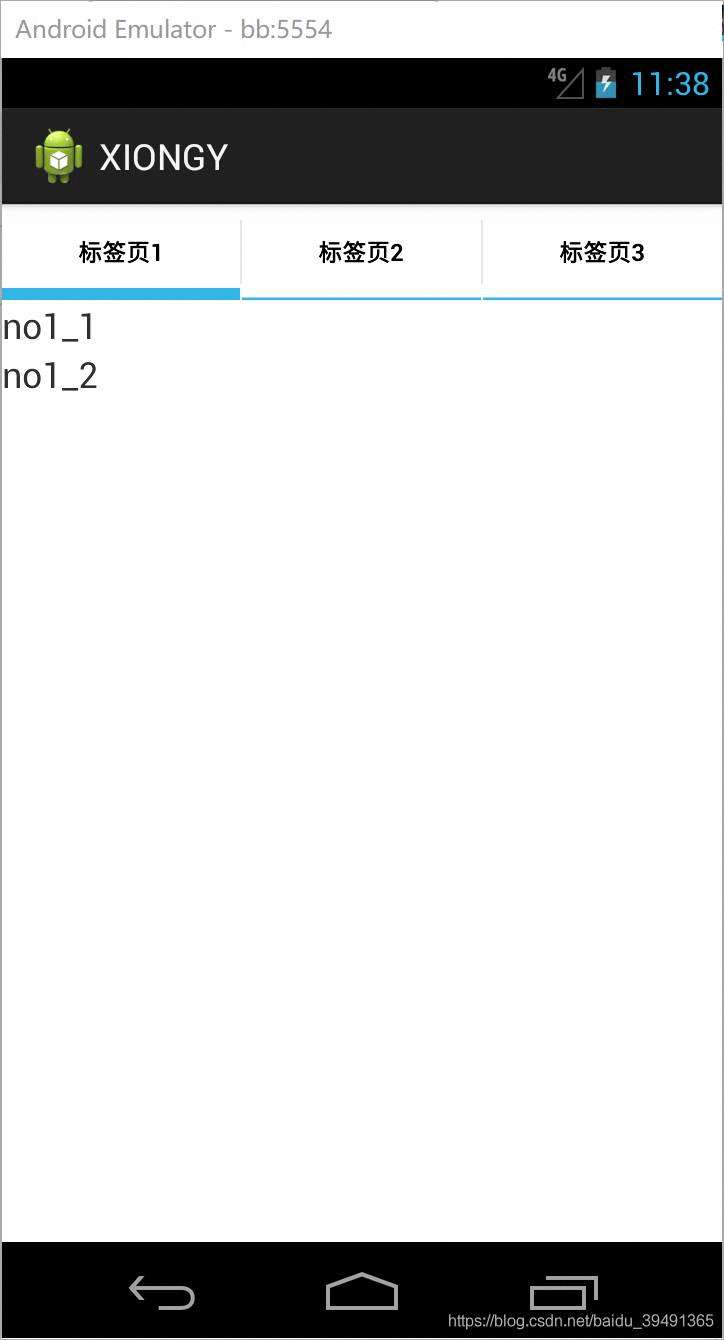

三、state machine viewer(状态机视图)

这个视图就比较显而易见了,他是在你的程序中如果综合出了状态机,对状态机各个状态之间的转化的示意图。如图3,你可以通过各状态之间的连线指示,直观的看出各个状态之间的转化,同时还可以从下面的真值列表中看出各个状态之间的转换以及转换条件,很快就可以判断程序的正确性。

四、chip planner(器件规划图)

该视图与Timing closure foorplan比较相似,功能也比较相近,但是他们之间也有一些区别,该视图能够更详细的看到各逻辑阵列块(EAB)的内部逻辑单元使用情况,同时能够估算出整个从某节点到输出的延时(这些都比较深入的应用了,还在摸索中,呵呵)如图4所示

timing closure floorplan

RTL viewer

state machine viewer

chip planner

各工具路径:timingclosure floorplan: assignment RTL viewer:Tools state machine viewer:Tools chipplanner:Tools

京公网安备 11010802041100号

京公网安备 11010802041100号