高速串行总线仿真(二)

仿真实例

1.探索多层板中的PCI-E串行通道

2.设置叠层以减小损耗

3.分析通道的不同配置对损耗的影响

4.检测驱动端规范

5.检查接收器规范

6.通过仿真得出整个通道的驱动约束限制

1.探索多层板中的PCI-E串行通道

在本节练习中,将探索在不同的通道配置下分析 PCI-Express多层板设计。

(1)打开HyperLynx.

(2)使用“File”一“Open Multiboard Project”来打开 Entire_System-pjh,路径如下:C:

\Adv_HL_Trng\SERDES_Interface \postlayout \MultiBoard

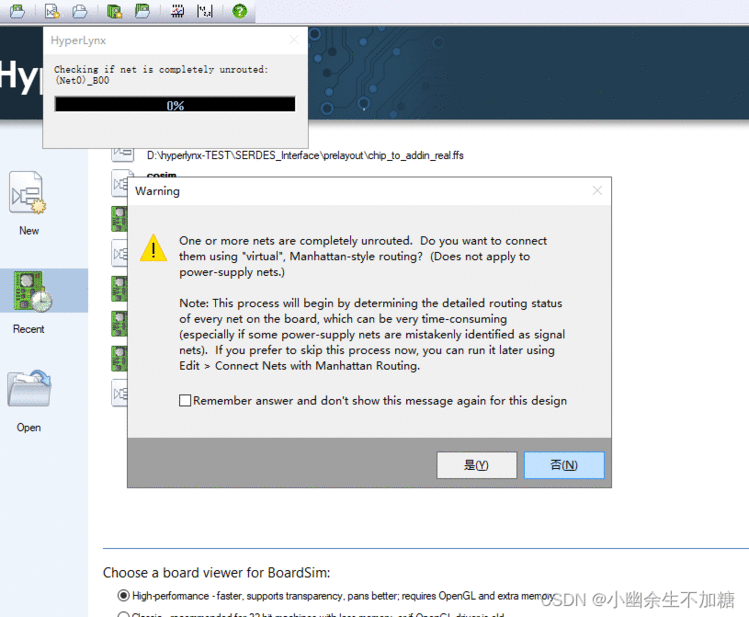

(3)当加载设计时遇到如图所示信息提示,选择“否”。

(4)通过“Models”→“Edit Model Library Paths”添加以下路径:C:\Ady_HL_Tng\SERDES_Interface\models。

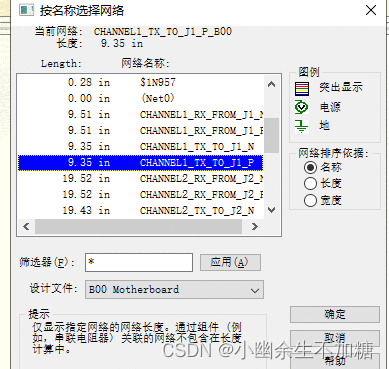

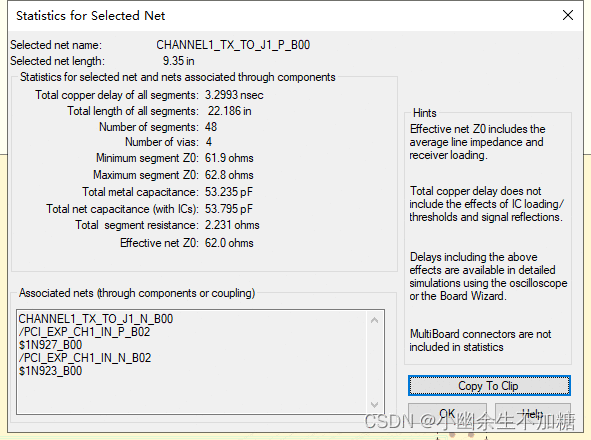

(5)选择网络“CHANNEL1_TX_TO_J1_P”,如图所示。

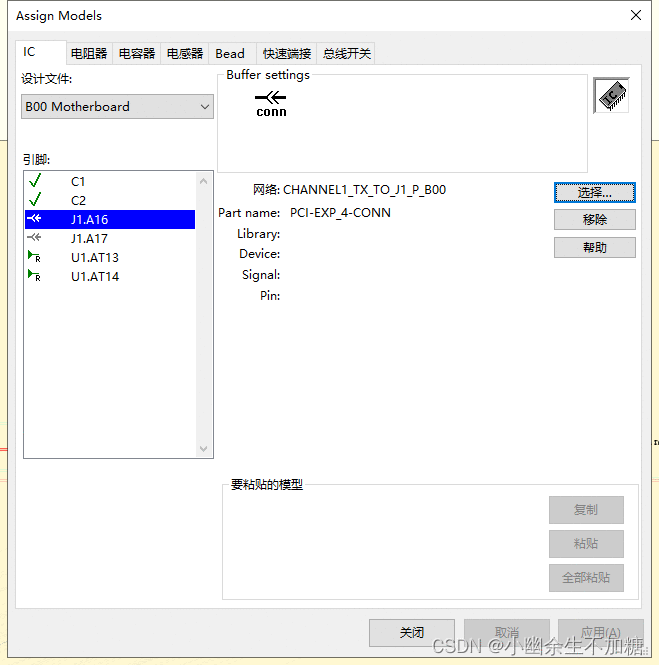

(6)单击按钮,查看网络的引脚信息,如图所示

(7)选择“Expot”→“Reports”→“Net Statistics”,导出的网络报告如图所示,由报告可以得到以下信息:

所有段的总延时:3.3337ns

所有段的总长度:22.186in

段的数量:48

过孔数量:4

最小段阻抗:62.7ohms

最大段阻抗:62.7ohms

总的接收容限:0.560pF

总的段阻抗:2.231ohms

有效网络电阻:62.7ohms

(8)选择网络CHANNEL2_TX_TO_J2_P。

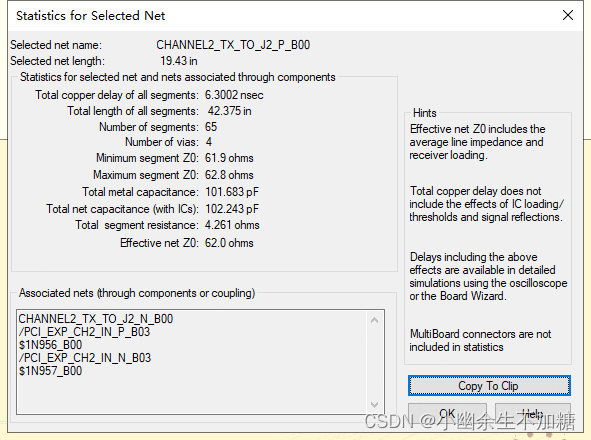

(9)选择“Export”一“Reports”→“Net Statistics”,如图所示,可以看出所有段的总长度是42.375in。

以上记录的长度包括差分对的网络长度,需要将其分成两段以便得到差分对的一个网

络。正如以上步骤显示,这个设计设置在多种不同的长度下进行仿真。

(10)保存BoardSim 会话,退出 HyperLynx。

2.设置叠层以减小损耗

在本节练习中,将要观察串行通道设计中影响损耗的因素。

设计要求如下。

层数:4

板厚:62mil

单端目标阻抗:60ohms

差分阻抗:100ohms

(1)打开一个新的 LineSim Free-Form Schematic,如图所示。

(2)确保启动了损耗仿真(提示:通过单击“Setup”→“Enable Lossy Simulation”或者单击菜单栏按钮)。

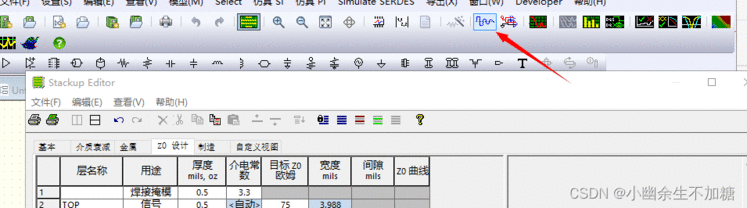

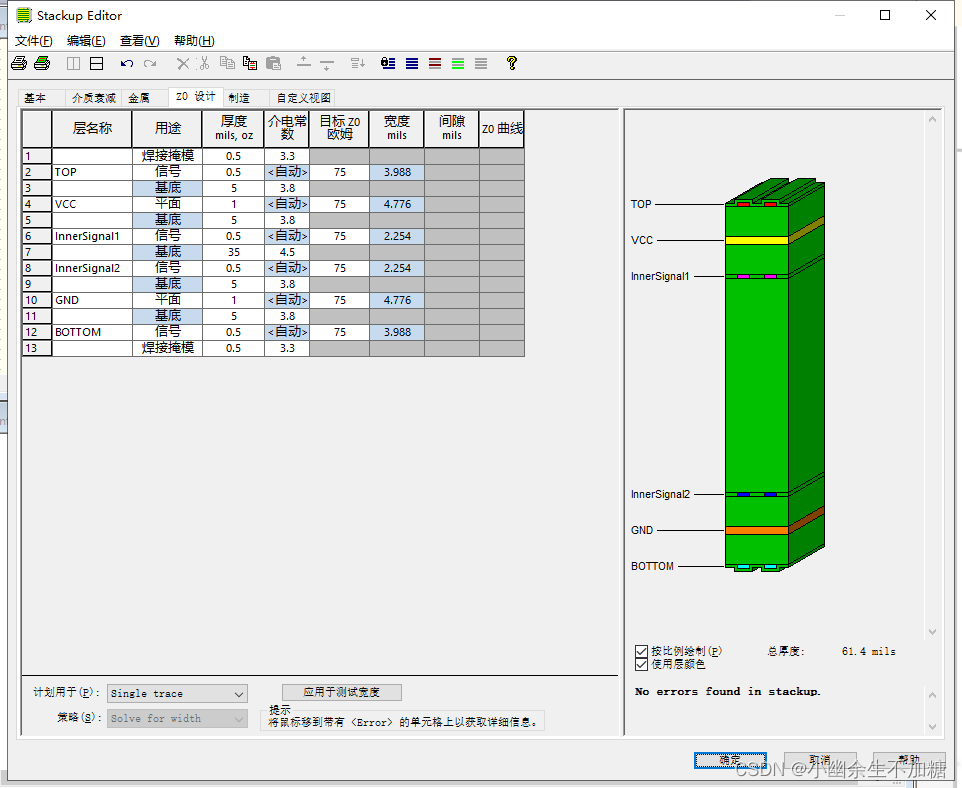

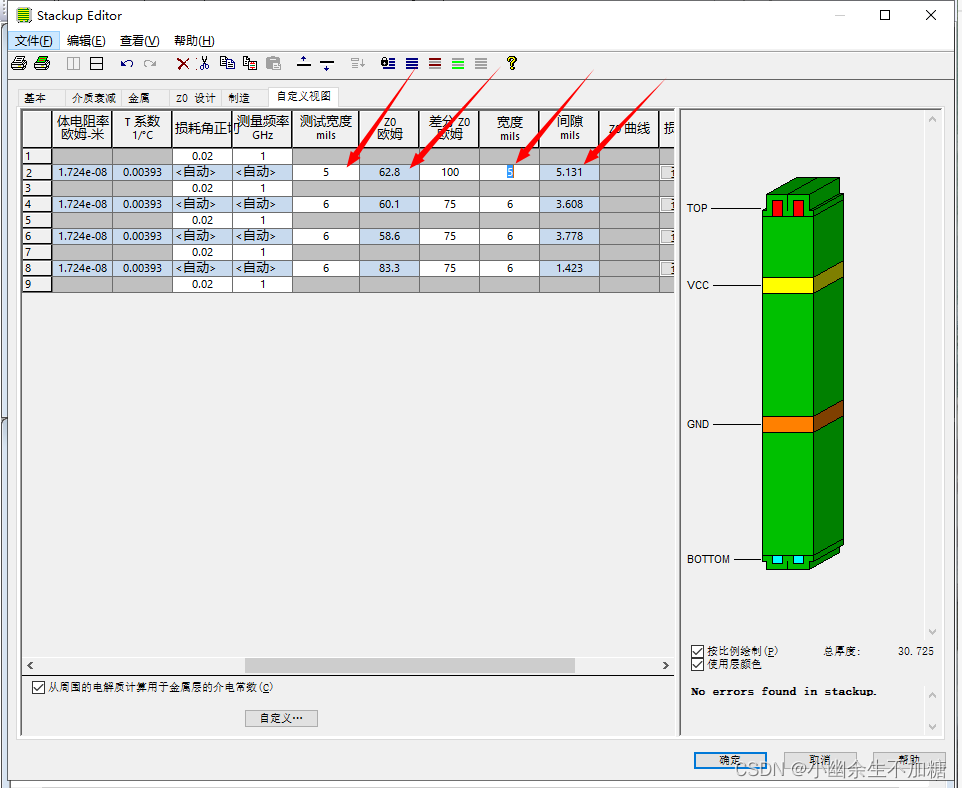

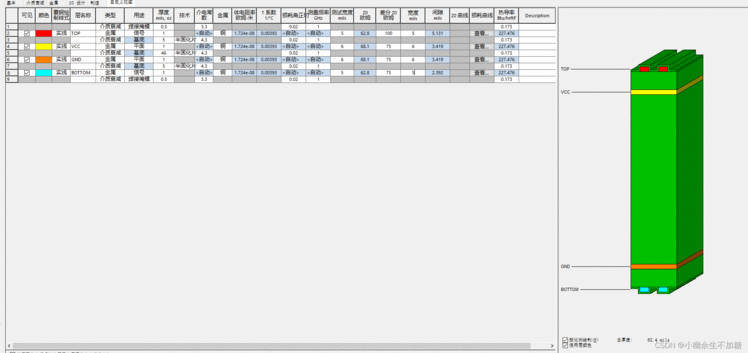

(3)打开叠层编辑器,单击“Z0 Planning”选项卡,如图所示。

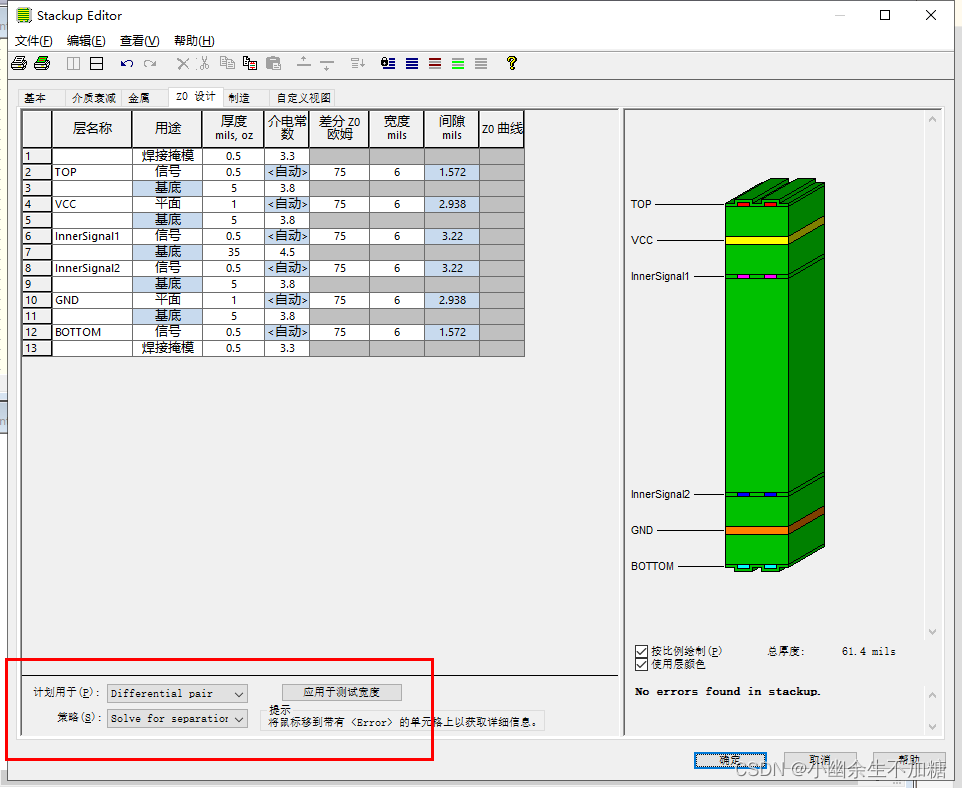

(4)在叠层编辑器对话框的左下角设置如图所示参数。

设计用途:Differential pair

方法:Solve for separation

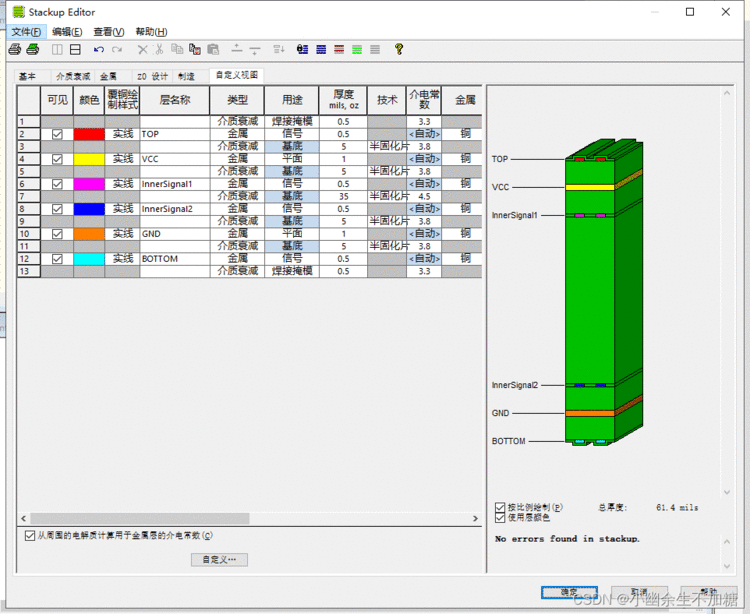

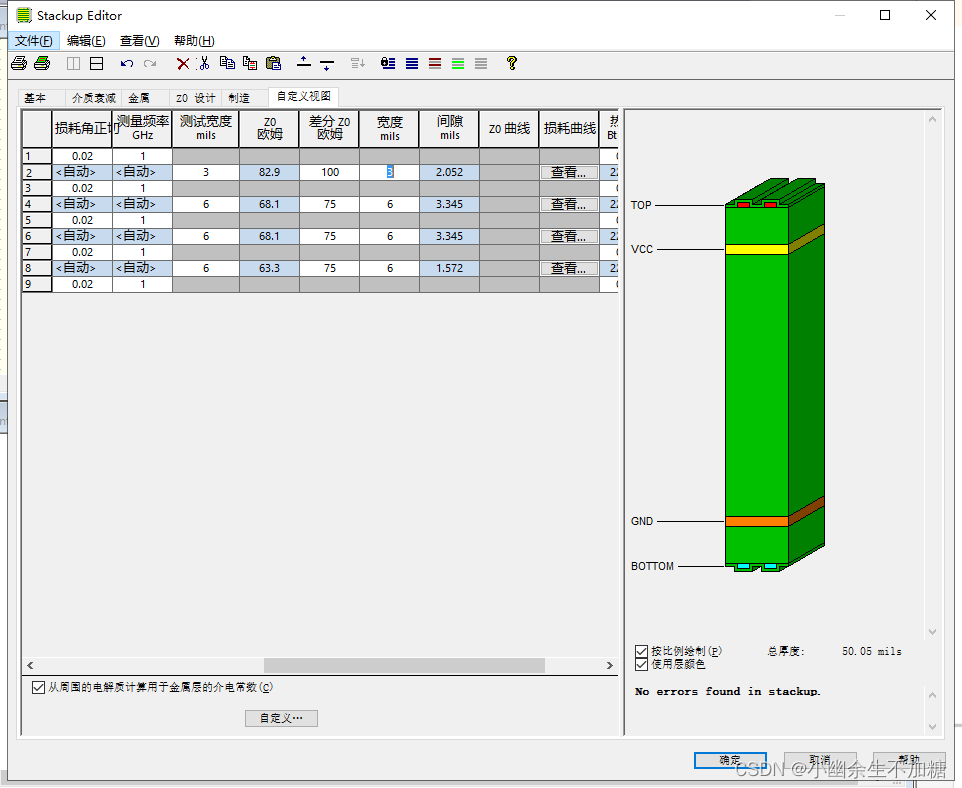

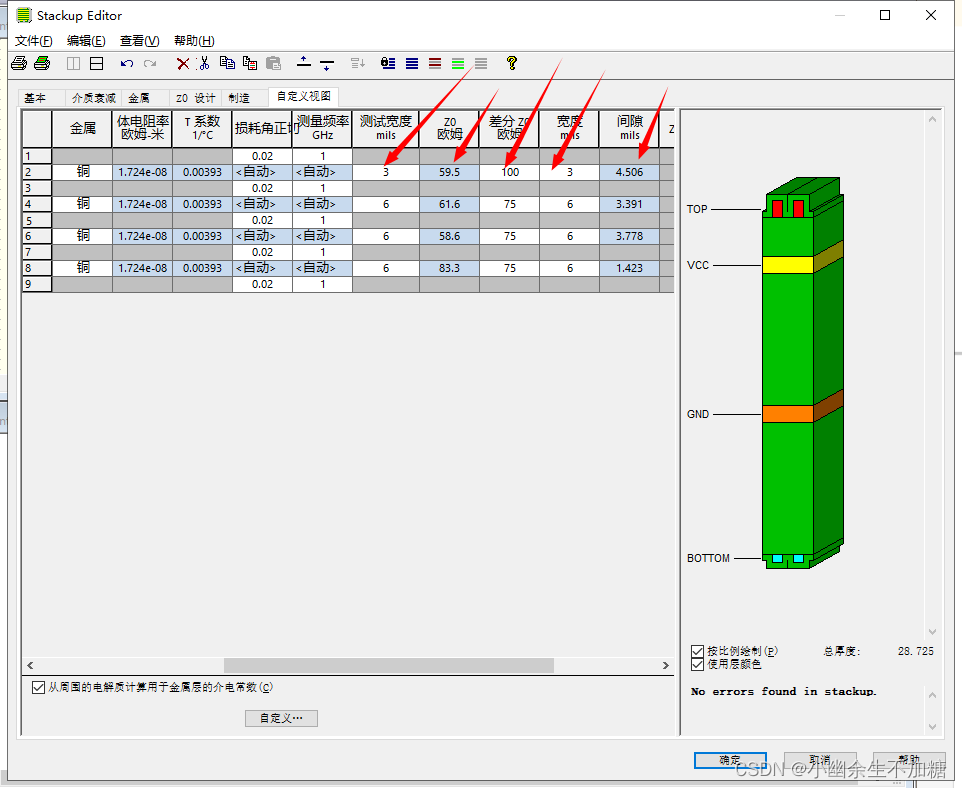

(5)选择“Custom View”选项卡,如图所示。

“Custom View”选项卡可以从其他选项卡进行访问,这个功能使得可以在一个选项卡下同时规划单端和差分阻抗。

(6)因为我们将要设计一个四层板,所以删除5、6、8、9层

①通过按下Ctrl键单击每层的行标题来选择5、6、8、9层,如图所示。

②)按Delete键删除。

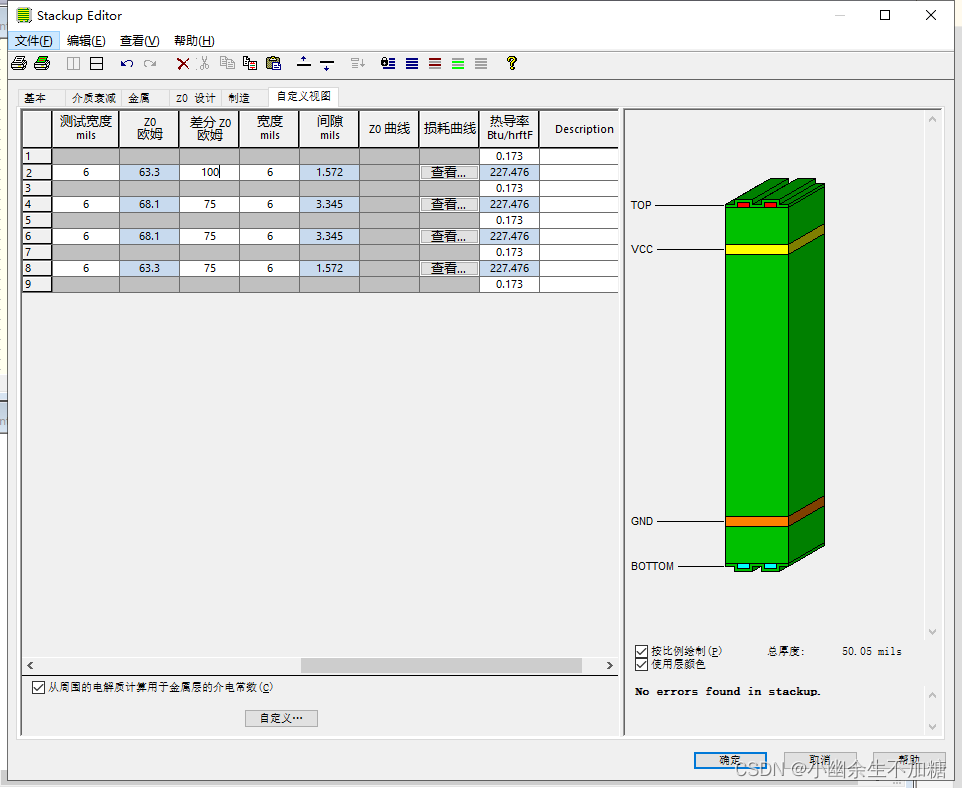

(7)在TOP层的“Dif Z0”列输入100,如图所示。记住,这是必需的差分阻抗。接下来看3mil线宽对损耗、阻抗、差分间距的影响。

(8)在顶层设置“Test Width”和“Width”都为3,如图所示。

正如所看到的,单端阻抗是82.9ohm,间隔是2.052mil。然而设计中需要的是 60ohm 的单端阻抗,这并没有达到要求的值,而且线间距太小不能满足生产的要求。

(9)在“Thickness厚度”列,为每一个指定的层输入以下信息。

Layer2(顶层):I(oz)

Layer3(位于顶层下的介电层):3(mil)

现在,60ohms单端阻抗已经达到,4.4mil的间距也可以接受,如图所示。接下来观察微带线的损耗。

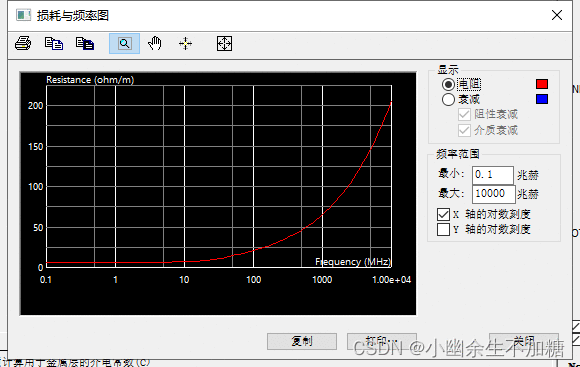

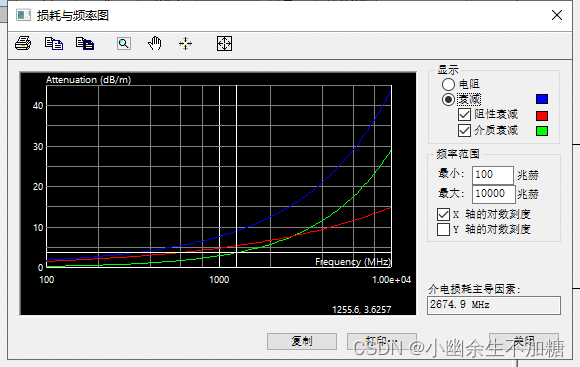

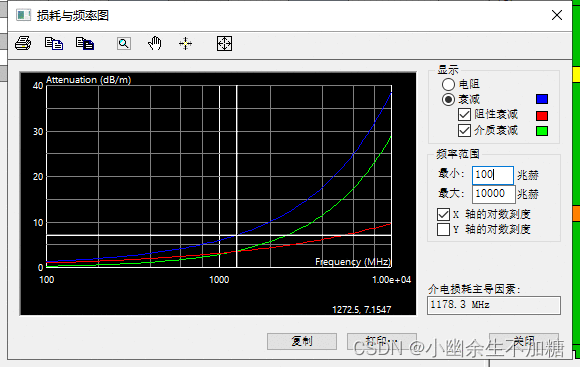

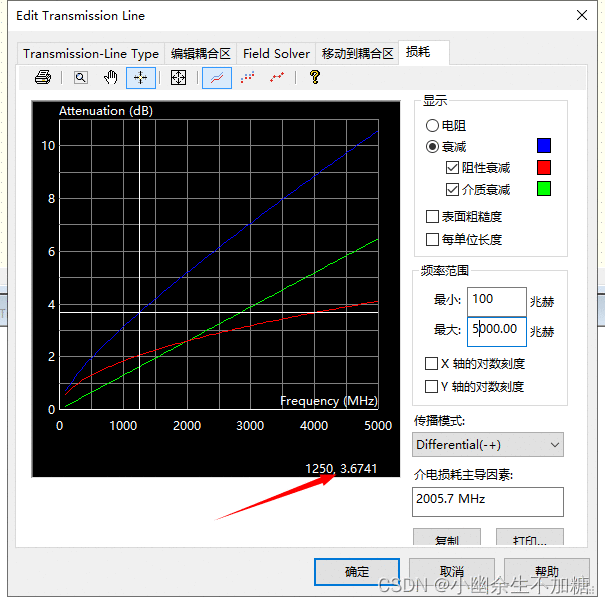

(10)单击顶层损耗曲线的“View”按钮,如图所示:

(11)在损耗图中,在1GHz附近用鼠标画框来观察。因为我们感兴趣的频率是1.25CHz,所以将在这个频率处查看损耗,如图所示。

(12)在图中,通过鼠标右键选择Track Cursor跟踪光标,蓝色的曲线是电阻和介电损耗的总和。

(13)将光标置于1250MHz 处,记录以下损耗(提示:在对话框的右下角显示鼠标指示的值):

在宽度为3mil、电介质厚度为3mil、损耗因素为0.02时的损耗为 10dB。

(14)关闭图形对话框。

(15)改变第3层的厚度为5mil,将顶层的“Test Width”和“Width”设置为5,如图所示。

(16)重复(11)~(13)的操作步骤,记录 1250MHz处的损耗。在宽度为5mil、电介质厚度为5mil、损耗因素为0.02时的损耗为8.0476dB,如图所示。

接下来确定影响损耗的其他因素。

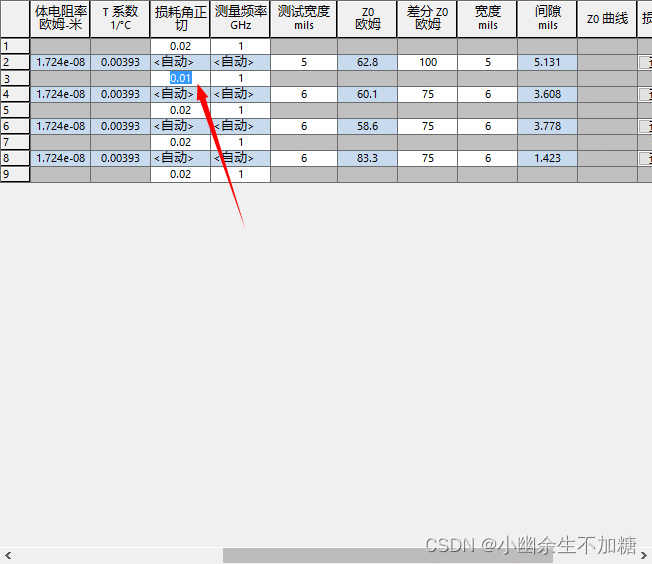

(17)在第3层的“Loss Tangent损耗因子”列输入0.01,如图所示。

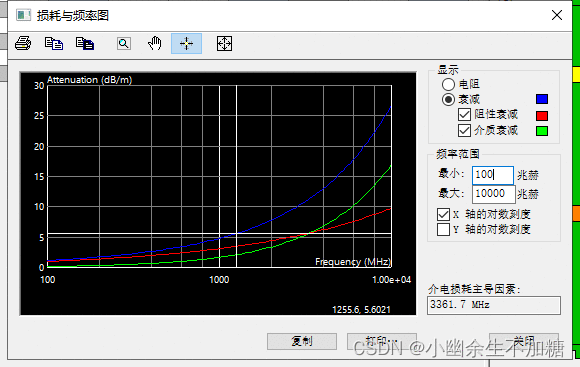

(18)重复步骤(11)~(13),记录1250MHz以下的损耗,如图所示。

可以看到,在宽度为5mil、电介质厚度为5mil、损耗因素为0.01时的损耗为6.6dB。

(19)通过上面的观察,对影响损耗的因素总结如下:

①随着电介质厚度的减小,损耗减小;

②随着线宽的增大,损耗减小;

③随着损耗因素的减小,损耗减小;

④随着线长的增大,损耗减小。

(20)改变第3层的损耗因素为0.02。

(21)第7层和第8层的金属和电介质厚度与第3层和第2层的一样。

(22)第5层厚度输人46,以达到62mil的板层厚度,最后的叠层应该如图所示。

(23)总结差分对的布线要求如下:

线参数 Diff Z0=100ohms,线宽为5mil,线间距为5mil。

(24)在叠层编辑器中单击“OK”按钮。

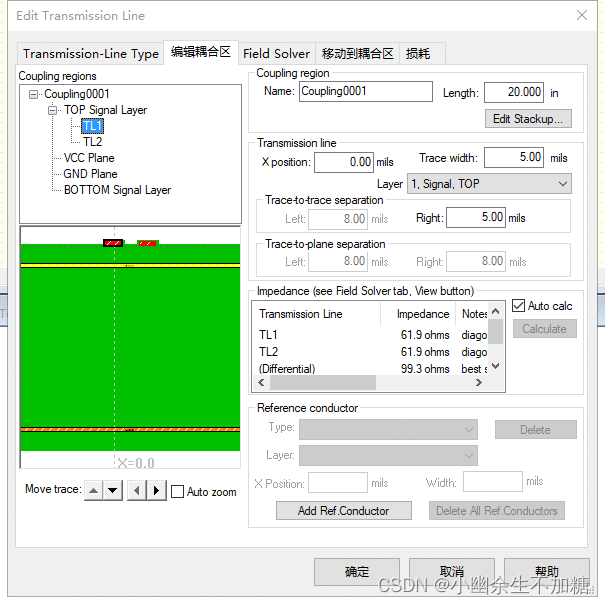

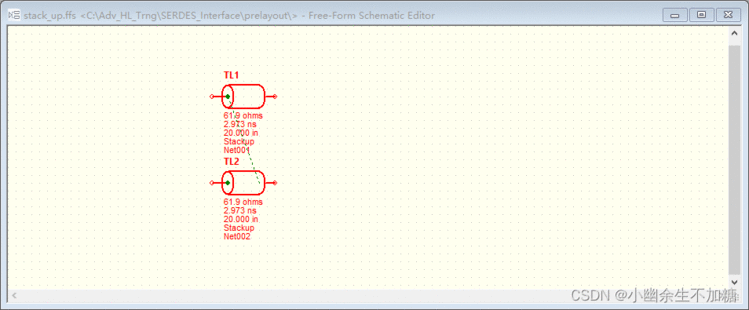

(25)在原理图中放置两个传输线符号,并使其耦合。

①选中两条传输线。

②单击鼠标右键选择“Couple”,每条线的宽度设置为 5mil,线间距设置为5mil,如图所示

(26)在编辑耦合区域的阻抗选项卡上,记录TL1、TI2和差分阻抗的值如下。

TL1 的阻抗:61.9ohms

TL2的阻抗:61.9ohms

差分阻抗:99.3ohms

(27)可以发现以上的单端阻抗和叠层编辑器中的Z0值略有不同。

(28)输入长度值为20in,如图所示。

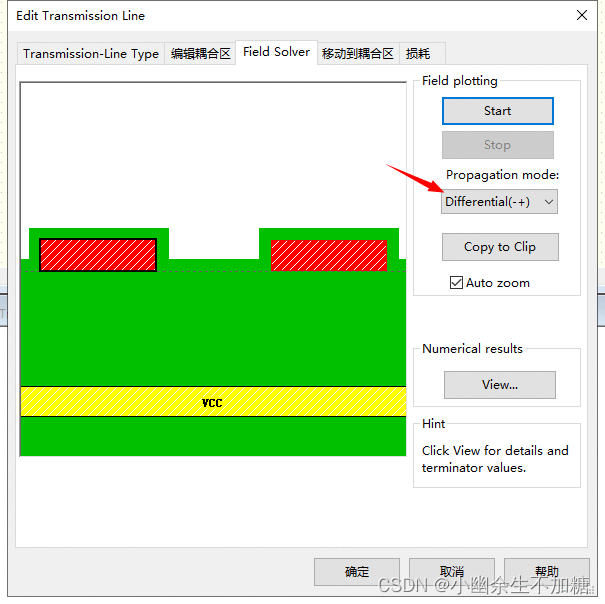

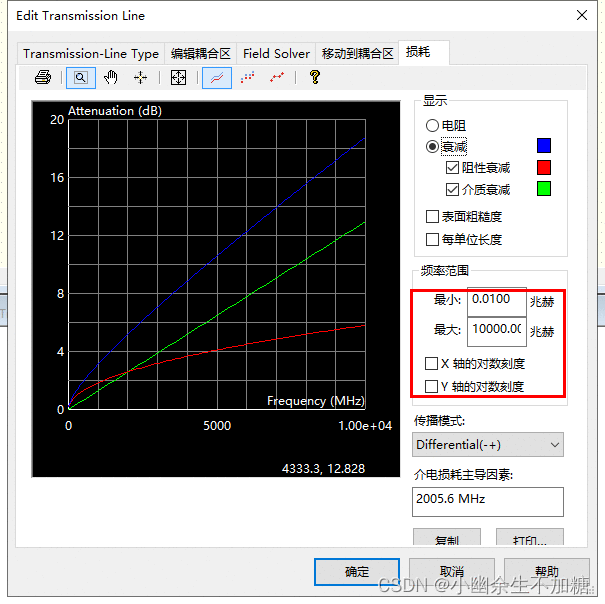

(29)单击“Loss”选项卡(确定损耗仿真被使能)。

(30)确保传输线模式区域设置为“Differential(±)”,如图所示。

(31)在X、Y两个轴上都关闭log scale*(对数刻度)*。

(32)确保“Per unit length每单位长度”选项不被选中。

(33)测量1250MHz的损耗并记录如下(注意:如果鼠标指示的值不显示,可放大并记录相对应的Y轴对应的值):在20in 差分对中的损耗为3.67dB,结果显示如图所示。

这是另一种查看损耗的方法,可以看到在“Per unit length”关闭的情况下这个指定长度的总损耗。此外还可以看到,损耗取决于传播的模式。

(34)保存文件在C:\Adv_HL_Tng\SERDES_Interface \prelayout 路径,文件名为 stack

up.ffs,如图所示。可以使用这个原理图作为前仿真的起点。

3.分析通道的不同配置对损耗的影响

在本节练习中,将对串行通道在不同配置下的插入损耗进行评估。

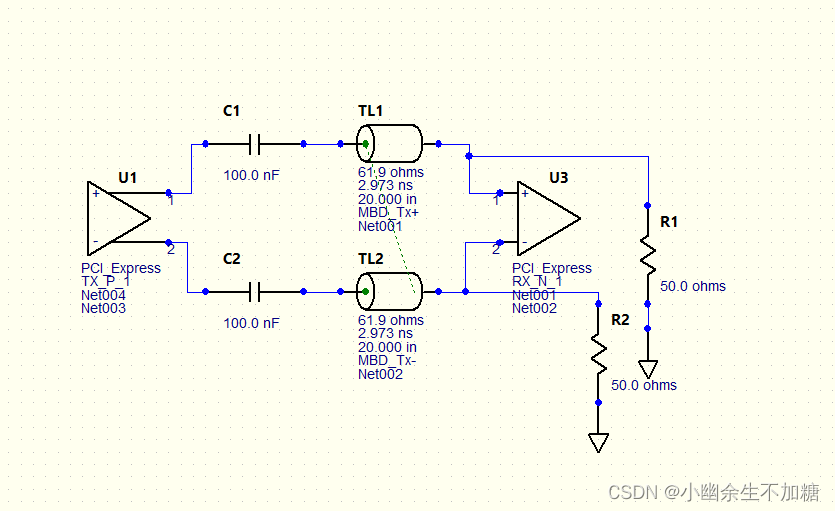

(1)从以下路径打开channel_simple.ffs 文件:C:\Adv_HL_Tmg\SERDES_Interface \prelayout,如图所示。

首先通过导出S参数模型来观察通道损耗。

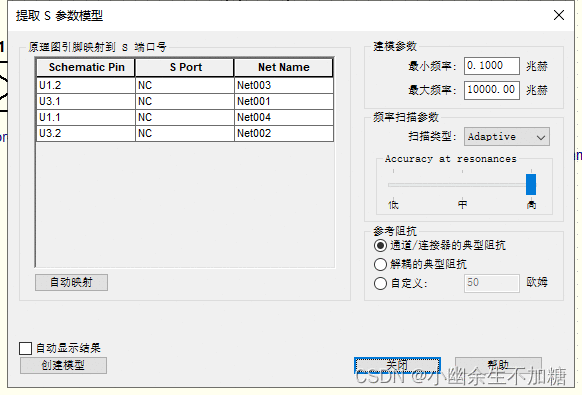

(2)选择“Export”一“S-parameter Model”,在打开对话框中输入参数,如图所示。

(3)单击“Create Model”按钮,打开如图所示对话框。

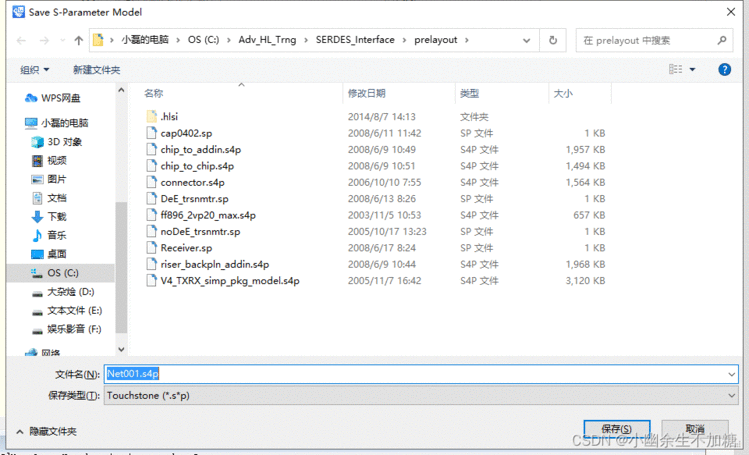

(4)在以下路径保存文件为 simple_channel.s4p;C:\Adv_HL_Tmg\SERDES_Interface\prelayout

.s4p 文件在Touchstone Viewer 中打开查看。

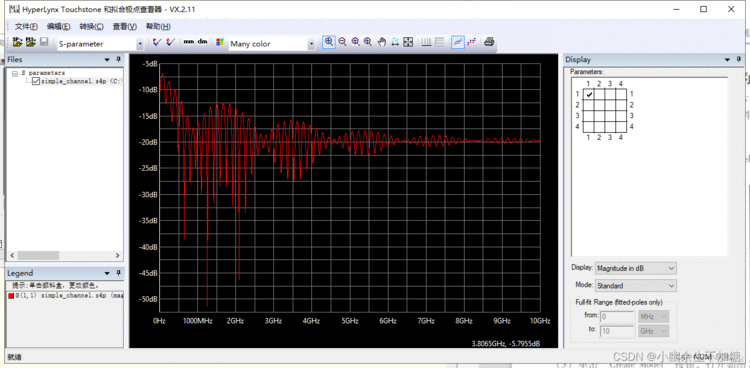

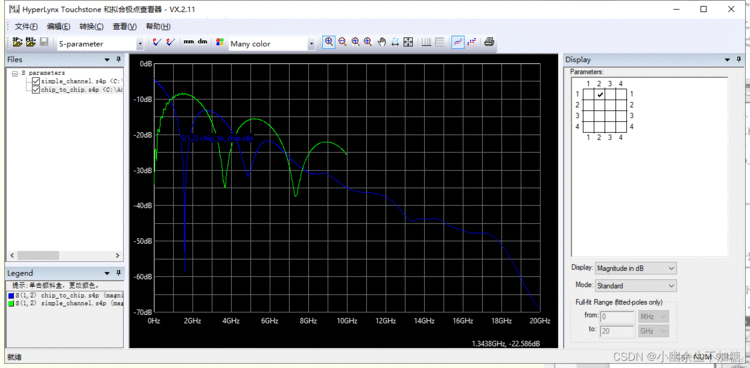

(5)在左侧窗口的参数列表中,关闭显示S11,打开显示S12(插入损耗),如图所示。

插入损耗S12:

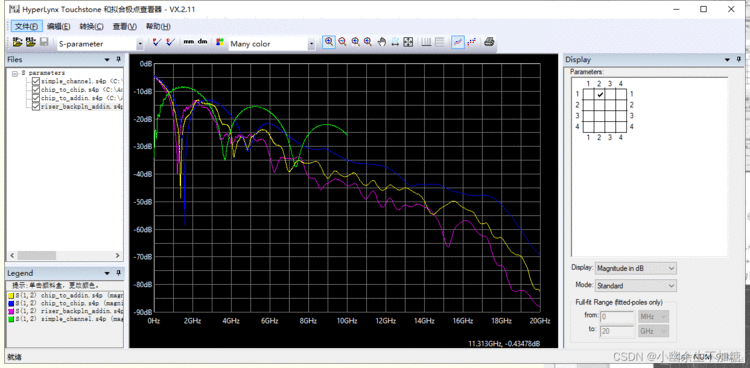

接下来,通过打开之前导出的.s4p文件来比较不同通道配置下的插入损耗。

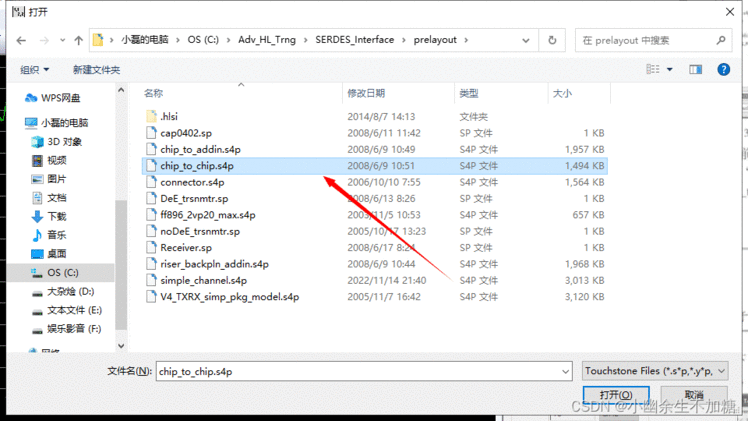

(6) 选择“File” →“Open Touchstone”。

从以下路径选择chip_to_chip.s4p文件:C:\Adv_HL_Tng\SERDES_Interface\prelayout。

这个通道的配置如下:驱动端一→封装→20in 微带线→封装→接收端。

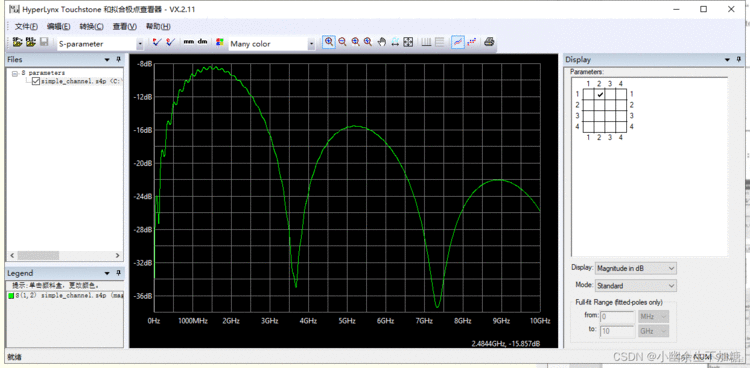

(7)重复步骤(5),以显示S12曲线,如图所示.

(8)重复步骤(6)和(7),以显示chip_to_addin.s4p和 riser_backpln_addin.s4p

chip_to_addin.s4p:驱动端→封装→20in 母板→连接器一3in Add in→Breakout 过孔→封

装一→接收端。

riser_backpln_addin.s4p:驱动端→封装一3in Riser一→连接器一20in 背板→连接器一→3in

Add in→Breakout 过孔→封装→接收端

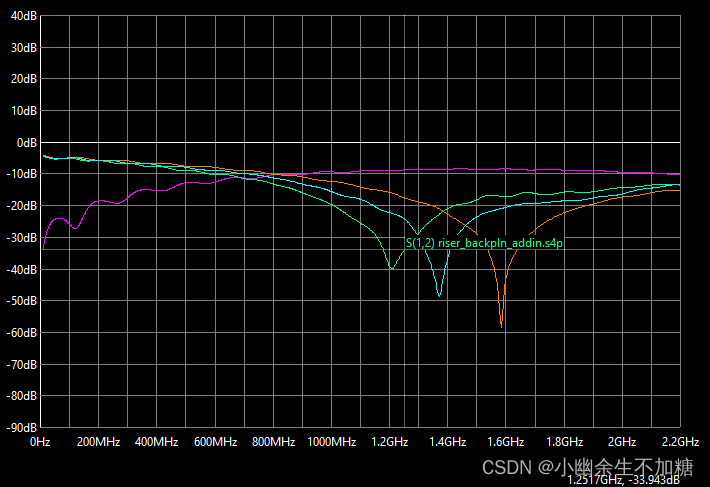

如图所示为四种通道的插人损耗曲线。

(9)放大插入损耗曲线图,以查看每个通道在1.25GHz处的损耗。

(10)通过图中的损耗曲线,可以看出 riser_backpln_addin.s4p 在1.25GHz 处的损耗最大。

(11)关闭所有打开的对话框,关闭原理图。

4.检查驱动端规范

在本节练习中,将仿真发射端连接到规定的测试负载以达到 PCI-E的眼图规范。

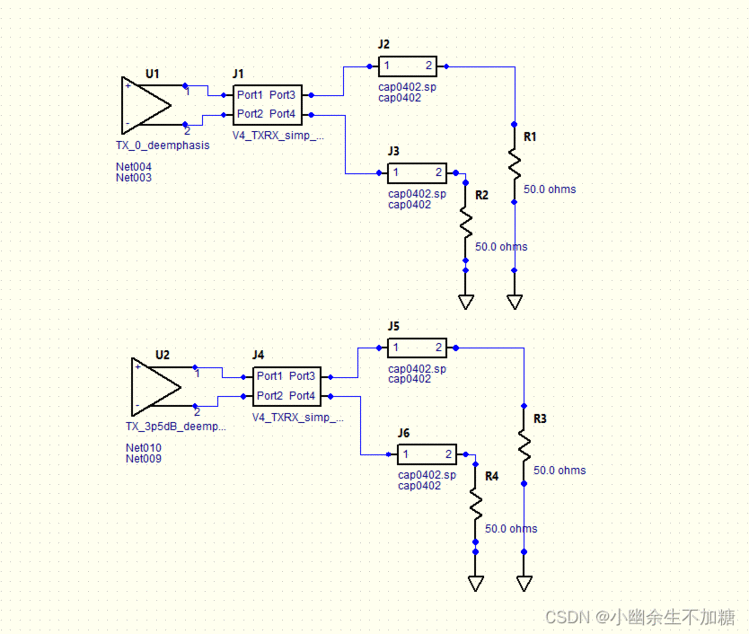

(1)从以下路径打开 validate_tx.ffs 文件:C:\Adv_HL_Tmg\SERDES_Interface \prelayout,如图所示。

在原理图中有两个测试电路,其中上面的驱动分配不具有去加重的模型,下面的带有去加重-3.5dB的驱动模型

(2)确认启用了损耗仿真,如图所示:

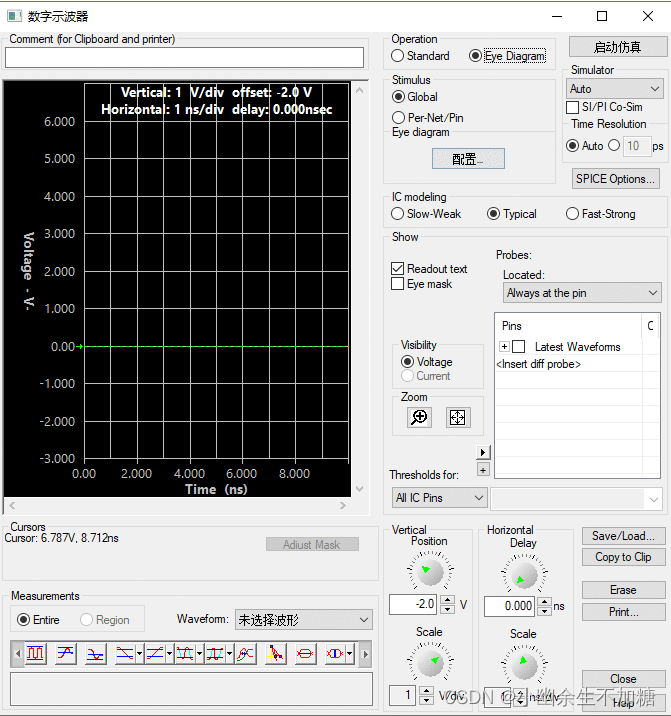

(3)打开示波器,选择眼图选项,如图所示。

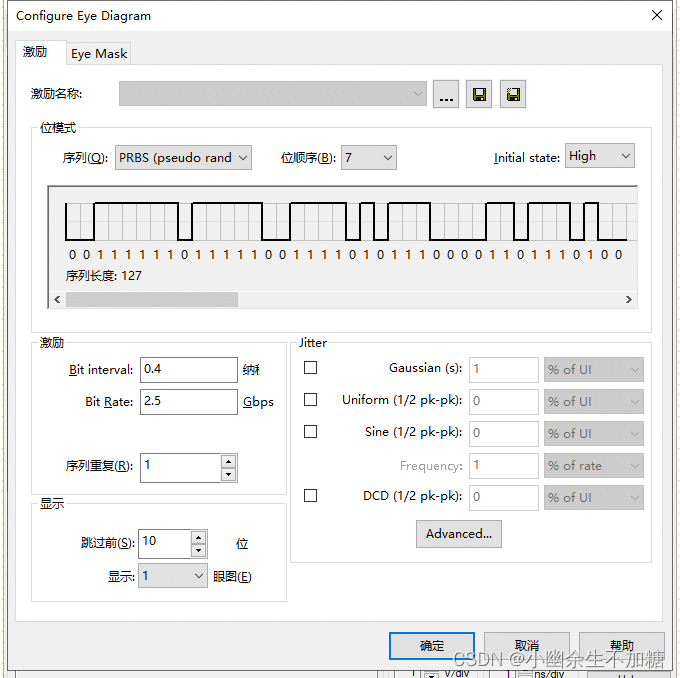

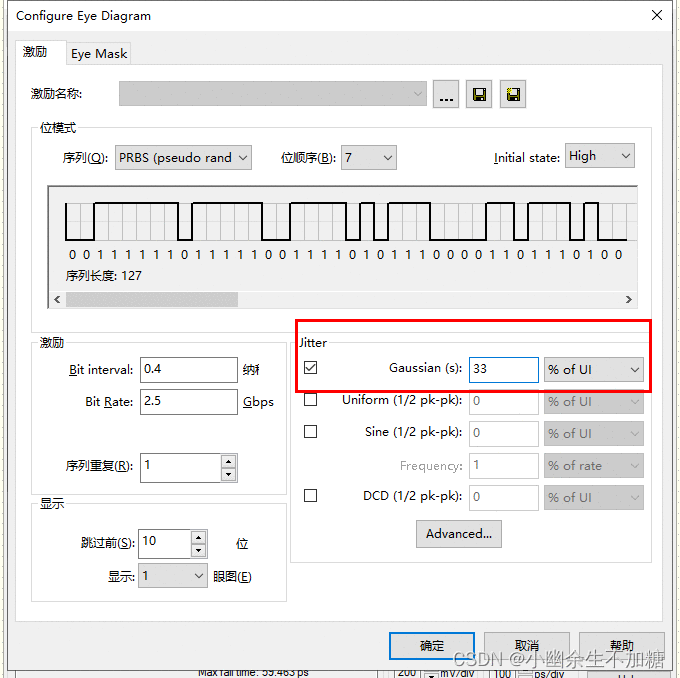

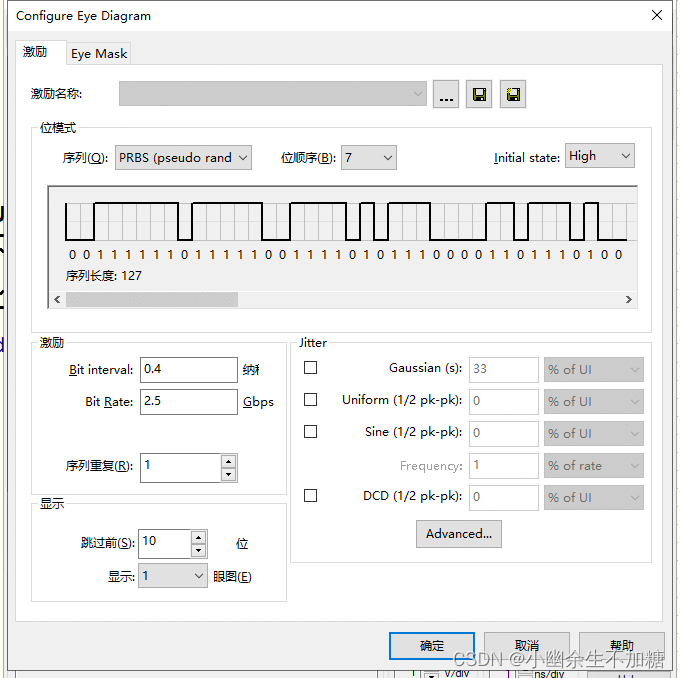

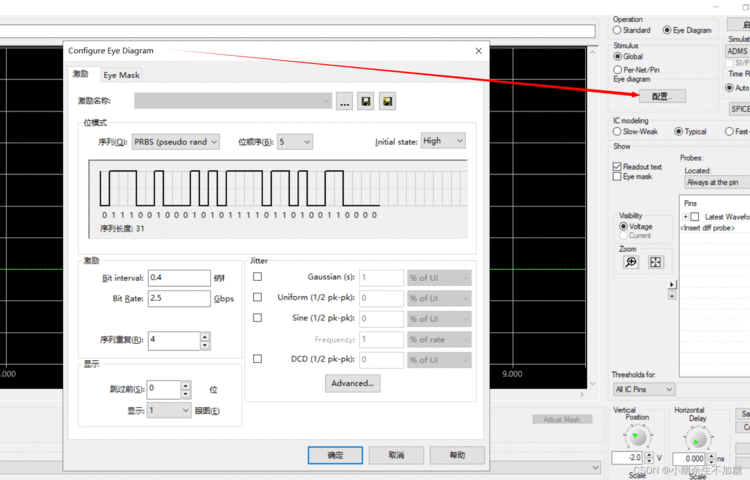

(4)单击“Configure”按钮,设置以下参数,激励设置如图所示,单击“确定”按钮。

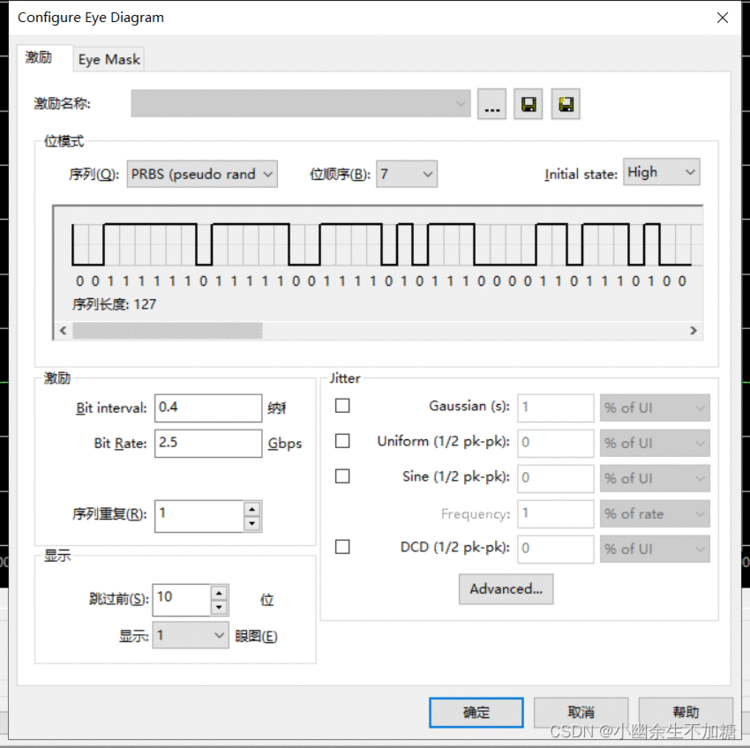

Sequence:PRBS

Bit Order:7

Bit Interval: 0.4ns

Sequence Repetitions:1

Skip First:10

Show:1eye

Random Jiter Amount: Ons

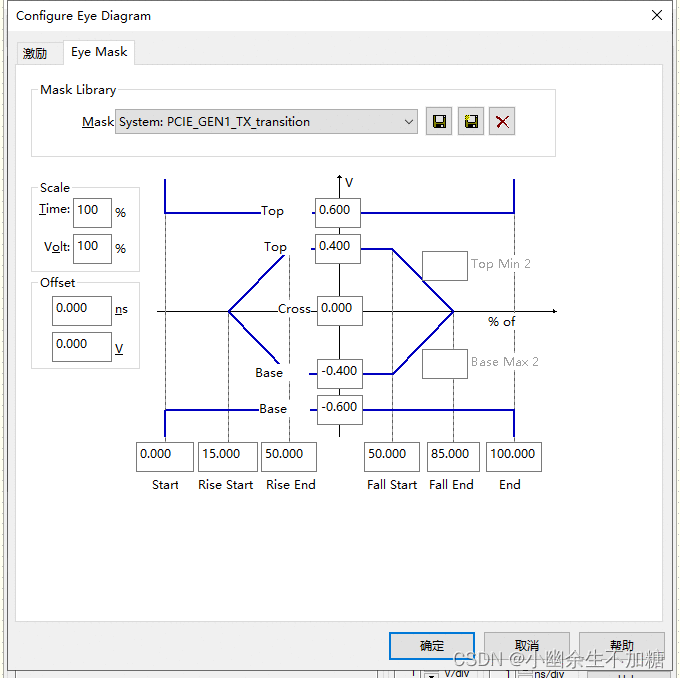

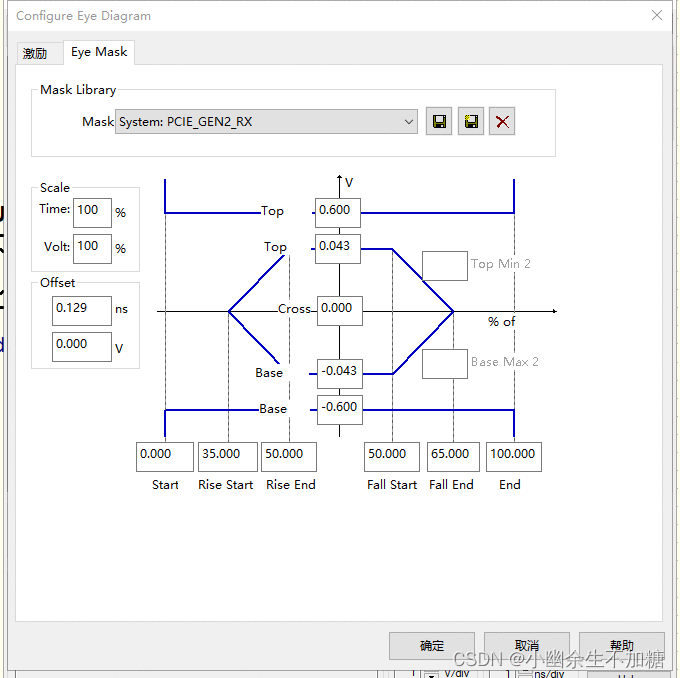

眼罩名称:System:PCIE_TX_Transition。眼罩选择如图所示。

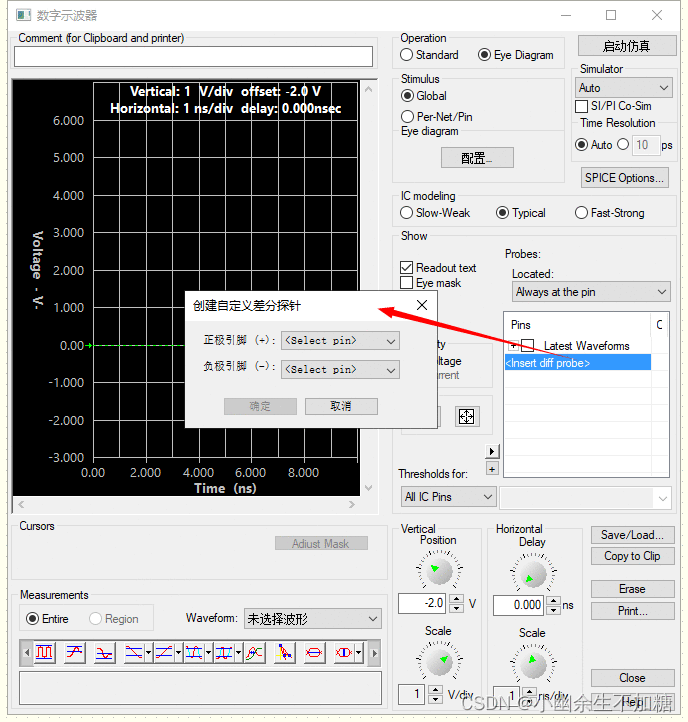

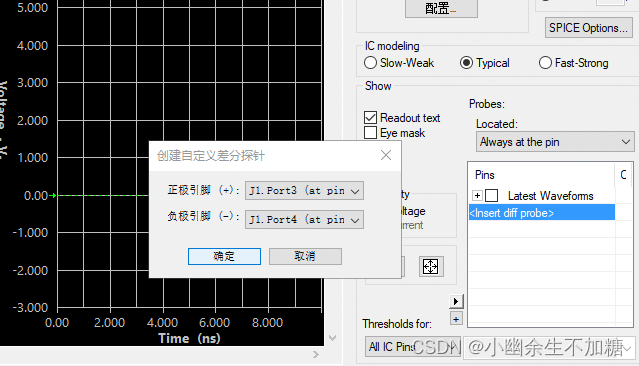

(5)在J1.Port3和J1.Port4插入差分探针,如图所示。

① 在探针选择区域双击“”。

②在出现的对话框中,选择“Positive pin”为“J1.Port3(at pin)”, “Negative pin” 为“J1. Pot4(at pin)”。单击“OK”按钮。

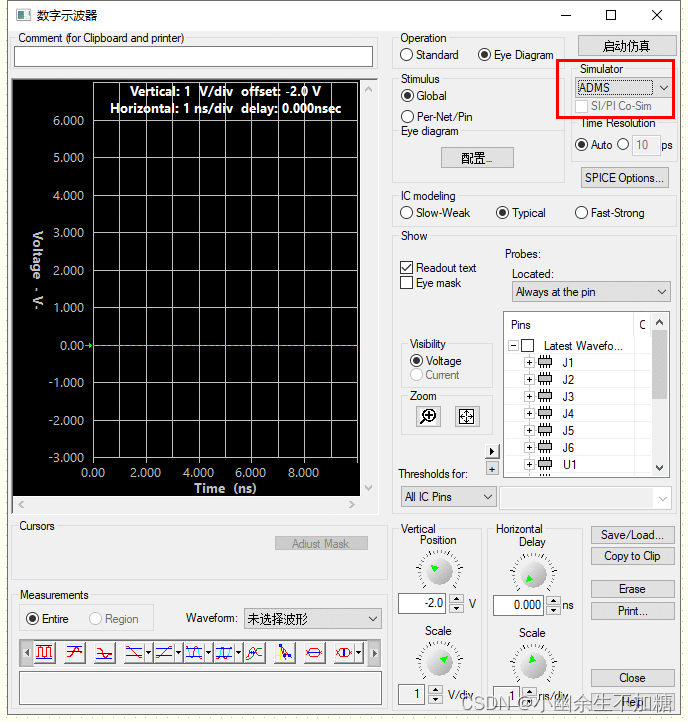

(6)选择Eldo/ADMS 仿真器

(7)单击“Start Simulation”按钮。

(8)在“Run ELDO/ADMS Simulation”对话框中,单击“OK”按钮。

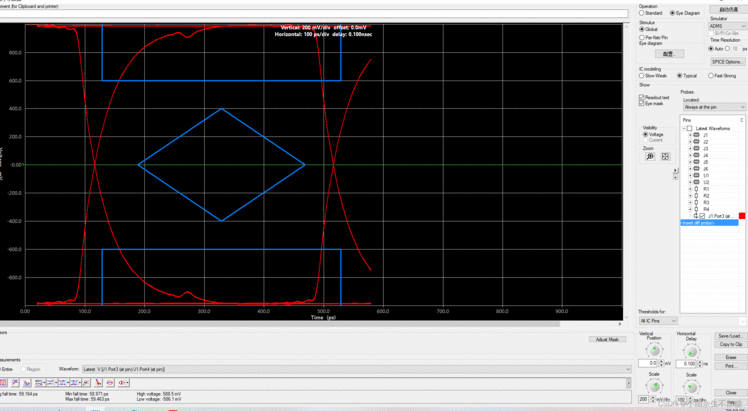

(9)调整水平和竖直标尺来查看眼图。

垂直位置:0

水平延时:0.1ns

垂直标尺:100mV/div

水平标尺:100ps/div

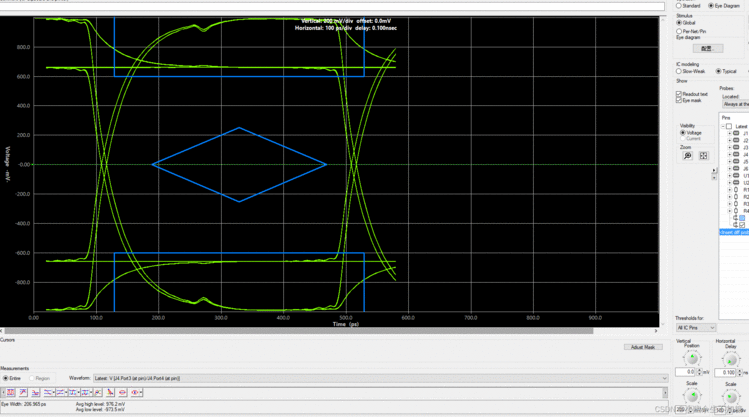

(10)在示波器的Zoom 区域选择,以查看眼图,显示调整眼罩。

①在 Show 区域选择“Eye Mask”

②单击“Adjust Mask”按钮。单击,拖曳眼罩到眼的中心,如图所示。可以看到,仿真波形达到了 PCI -E_Tx_Transition 眼罩的要求。

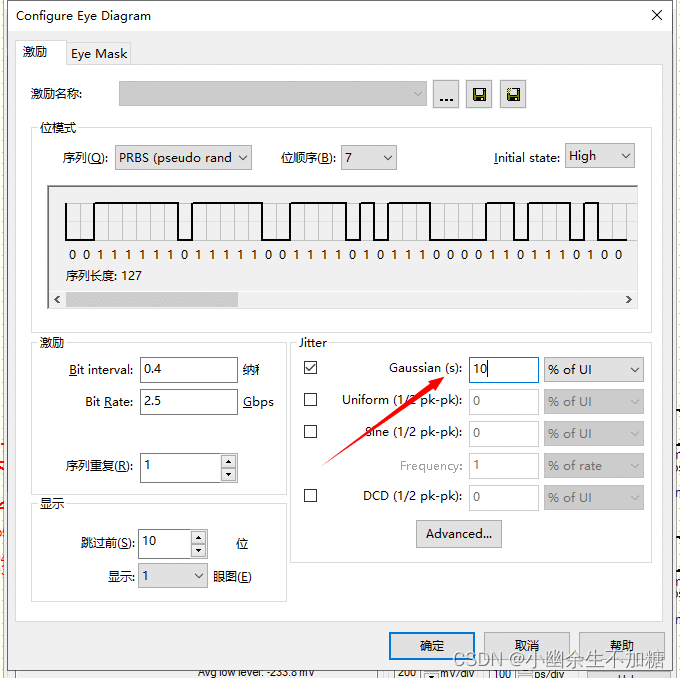

(11)给激励添加抖动(提示:“Configure”→“Stimulus”选项卡),如图所示,然后单击“OK”按钮。

(12)再次单击“Starnt Simulation”按钮,单击“OK”按钮。

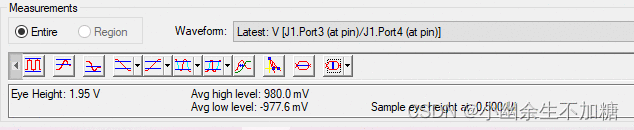

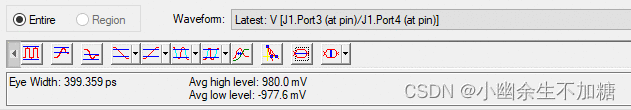

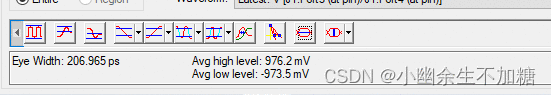

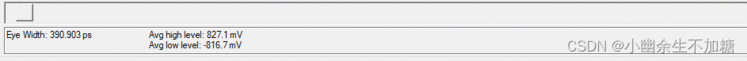

(13)测量眼宽和眼高,如表所示。

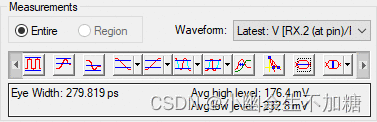

(12)再次单击“Starnt Simulation”按钮,单击“OK”按钮。

(13)测量眼宽和眼高,如表所示。

接下来,对加有3.5dB预加重的驱动端进行仿真,查看其是否符合规范。

(14)单击“Erase”按钮删除之前存在的波形。

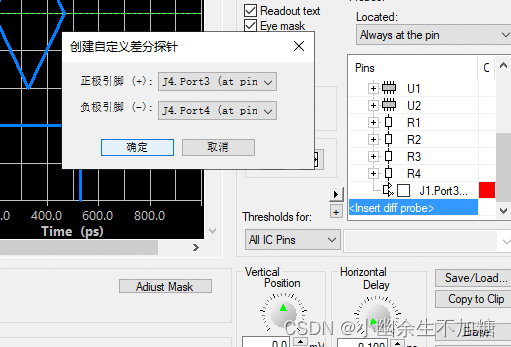

(15)在J4.Port3 和J4.Port4插入一个差分探针。

①在探针选择区域双击“”

② 在弹出的对话框中,选择“Positive pin”为“J4. Port3(at pin)”,“Negative pin”为“J4. Port4(at pin)”,如图所示。

③单击“OK”按钮。

(16)确保只有J4.(Port3)/(Porn4)探针被选中。

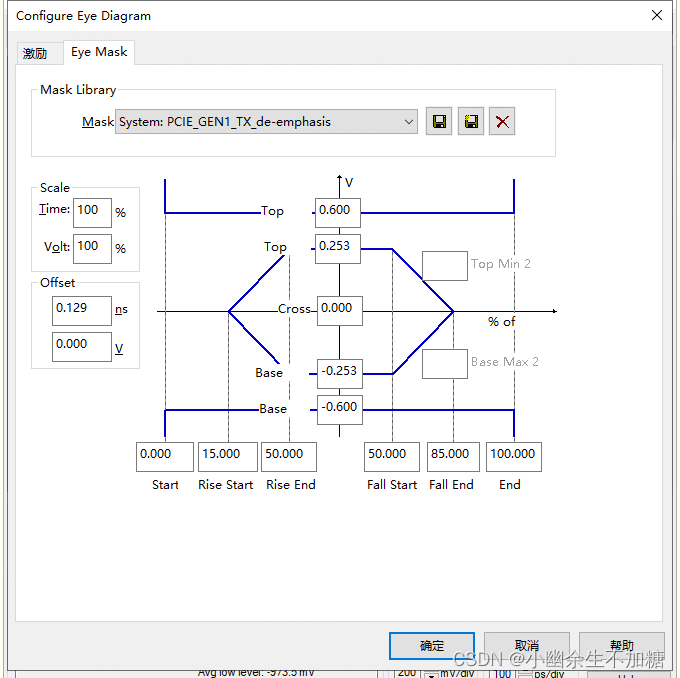

(17)在“Configure Eye Diagram”对话框的“Eye Mask”选项卡中,选择“PCIE_TX_de -emphasis”眼罩,如图所示。

(18)单击“Start Simulation”按钮,在接下来的对话框中单击“OK”按钮。

(19)调整“Horizontal Delay”的值,使它能够显示整个眼图,调整眼罩使其位于眼的中心。

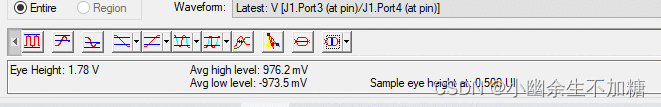

(20)测量眼宽和眼高,如表所示。

5.检查接收器规范

在本节练习中,将通过通道长度的变化来查看接收端的信号变化。

(1)打开 validate_rx.ffs 电路图,如图所示。

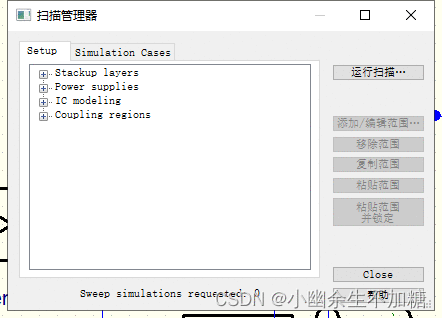

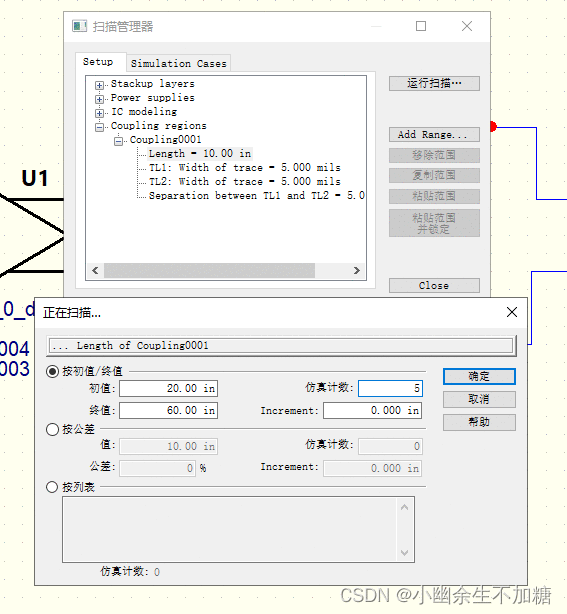

(2)选择“Simulate SI”→ “Run Simulation Sweeps”,打开如图所示对话框。

(3)设置扫描Coupling0001线长在20~60in之间,增量为10in。

①展开“Coupling regions”类别。

②展开“Coupling0001”。

选择长度 Length = 10in。

单击“Add Range”按钮。

输入参数,如图所示,单击“OK”按钮。

单击“Run Sweeps”按钮

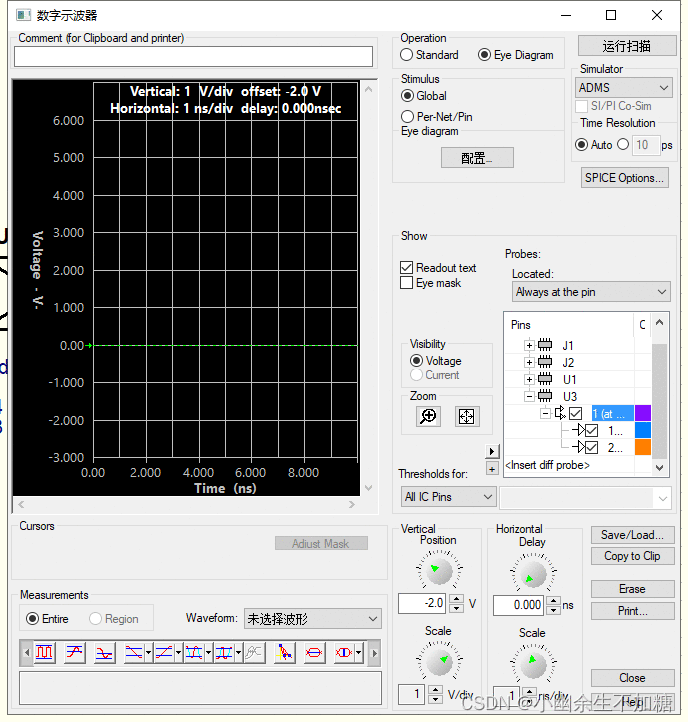

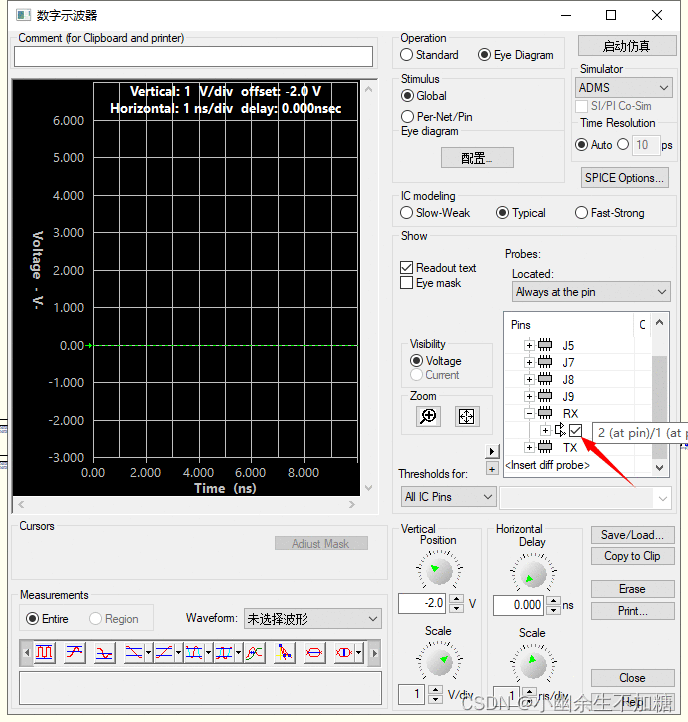

(4)在示波器中启用眼图选项,如图所示。

(5)单击“Configure”按钮,设置以下参数,设置激励如图所示,眼罩选择如图所示。

(6)关闭对话框。

(7)启用Eldo/ADMS选项。

(8)启用 U3 的差分探针,单击“Start Sweeps”按钮。

(9)通过选择探针引脚查看一个扫描波形,探针设置如图所示。

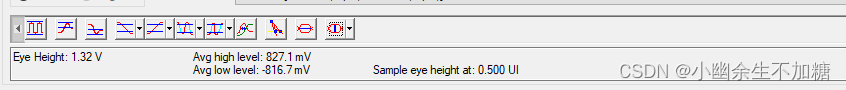

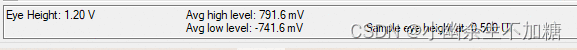

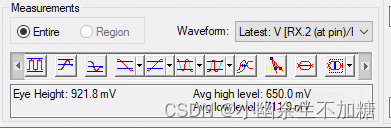

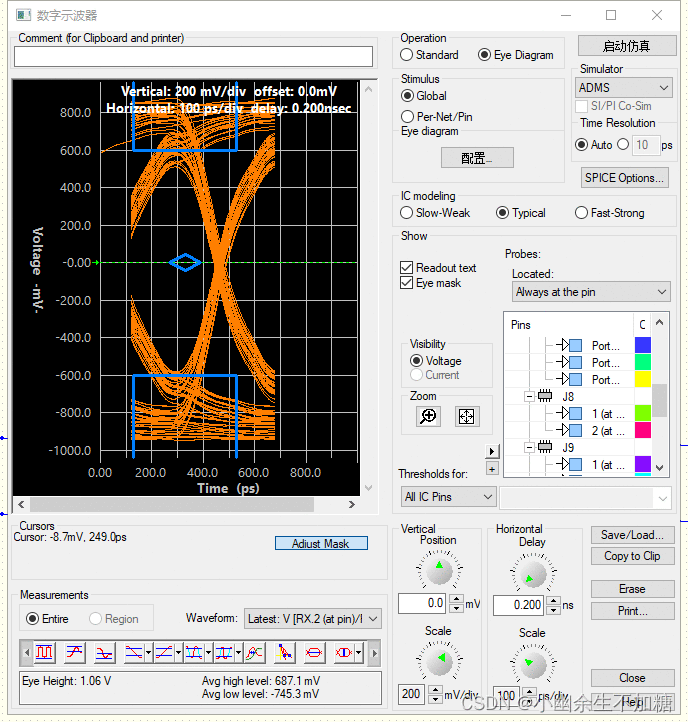

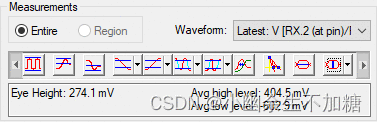

(10)在示波器中,得到的眼图如图所示。

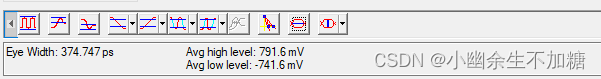

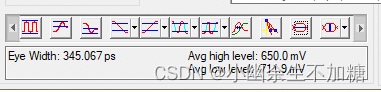

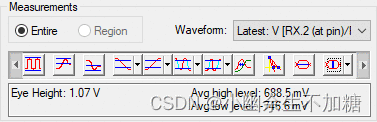

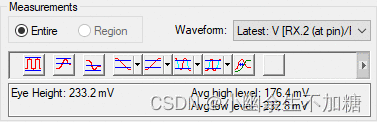

(11)使用自动测量来测量眼宽和眼高,如图所示。

(12)由图可见,随着通道长度的增加,接收端的眼逐渐闭合。

6.通过仿真得出整个通道的驱动约束限制

在本节练习中,将在LineSim 中对实际通道环境进行仿真,利用改变线参数和过孔参数

来改善接收端眼图质量。

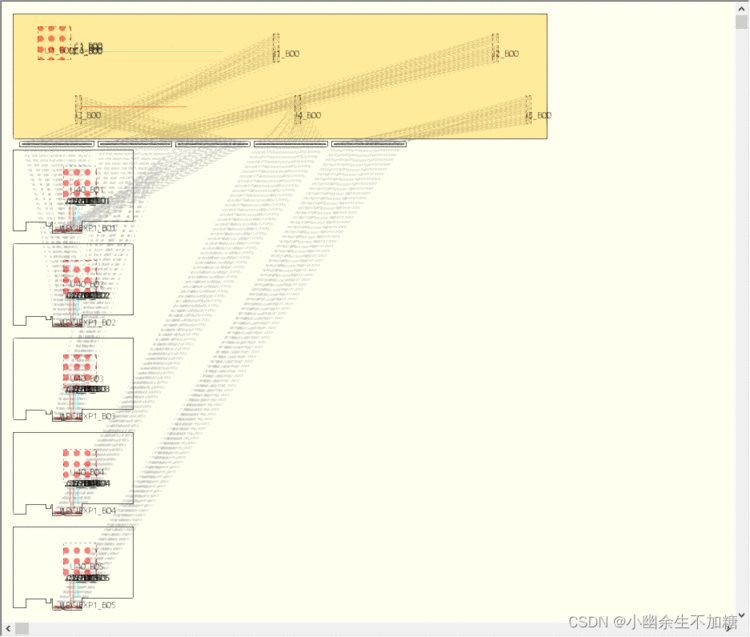

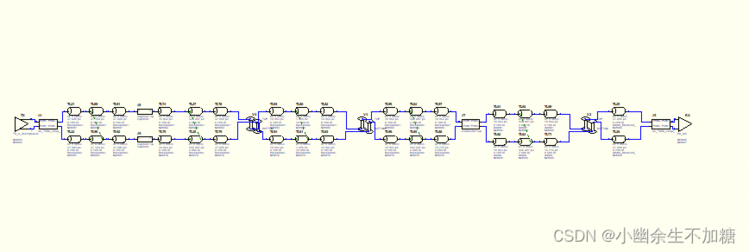

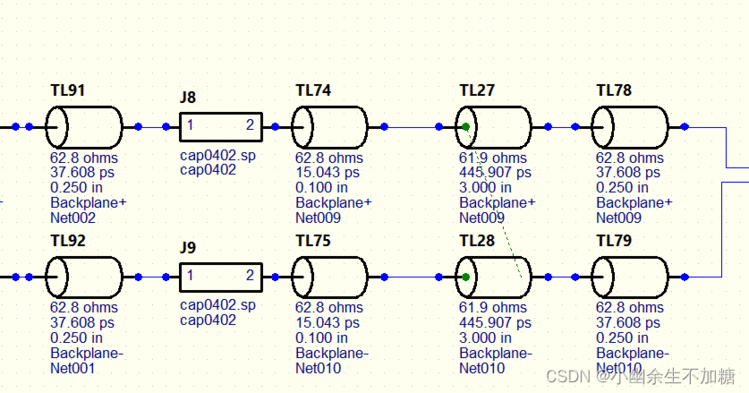

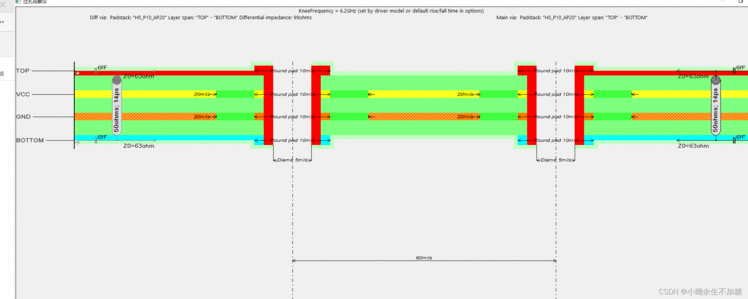

(1)在LineSim 中打开 chip_to_addin_real.ffs 文件,如图所示。

网络是从背板上的驱动端通过连接器连接到接插件的接收端,驱动和接收端的封装模型

用于生成整个通道的寄生参数。背板上有两个过孔,接插件上有一个过孔。

(2)观察网络的设置,记录下一些能够改善1.25GHz处信号传输的因素。

接下来,在当前的设置下选择网络来观察眼图质量。

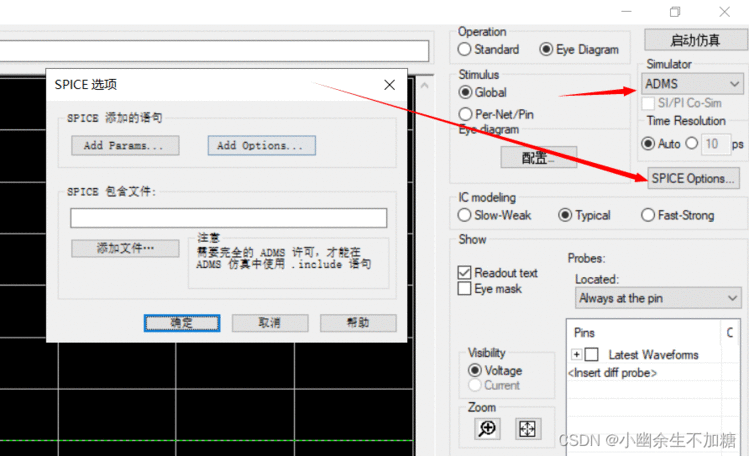

(3)在示波器中启动Eye Diagram Simulator,选择 ADMS 选项。单击 SPICE Options,设置如图所示。

(4)单击“Configure”按钮,设置以下参数,如图所示。

Sequence:PRBS

Bit Order:7

Bit Interval: 0.4ns

Sequence Repetitions: 1

Skip First:10

Show:1eye

Random Jitter Amount: 0% of unit interval

眼罩名称:System:PCIE_RX

(5)选择差分探针RX,如图所示。

(6)单击“Start Simulation”按钮。

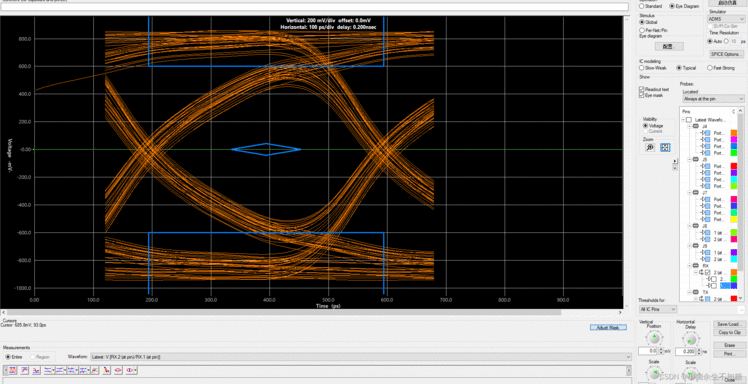

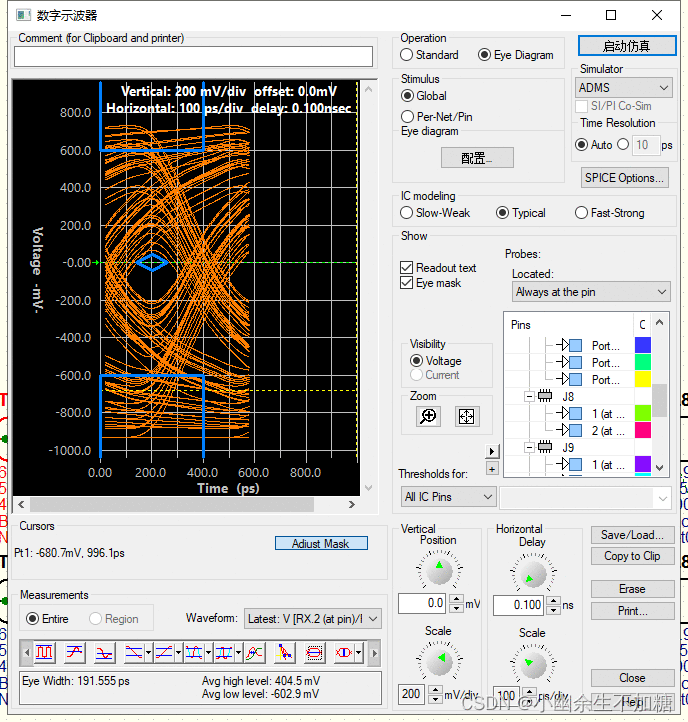

(7)调整水平延时,使眼图位于中间位置。单击“Eye Mask”显示眼罩,调整眼罩的水平刻度使之位于中心,如图所示。

正如图中所示,眼几乎通过了眼罩。但是还需要进一步改善眼图质量,因为此时还没有加入任何的抖动。

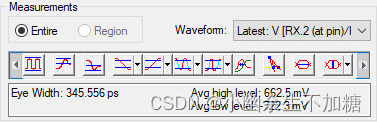

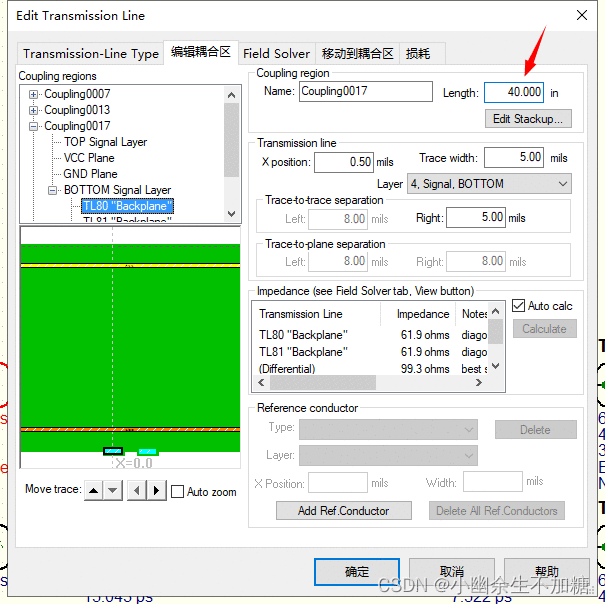

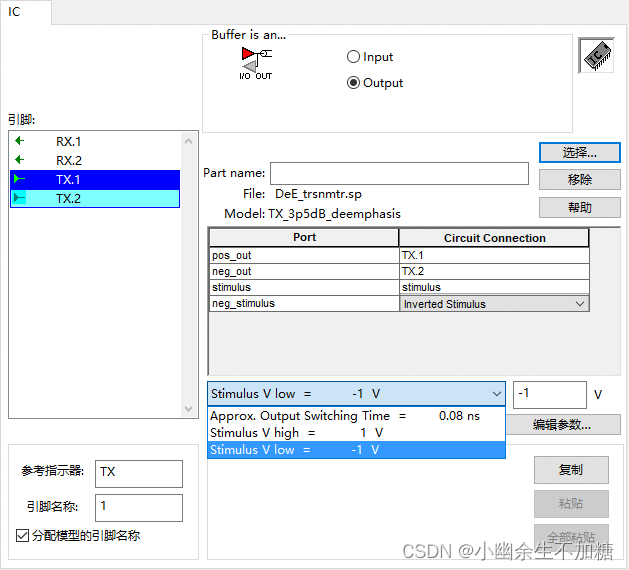

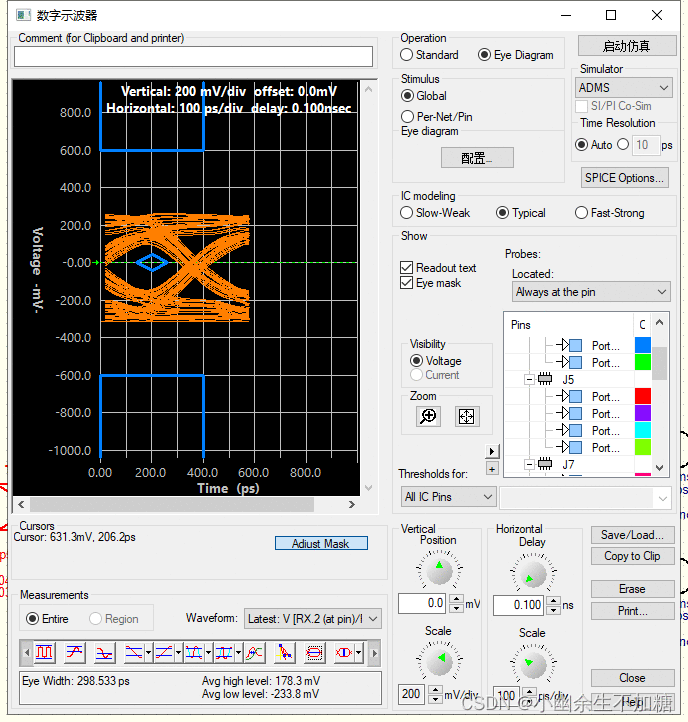

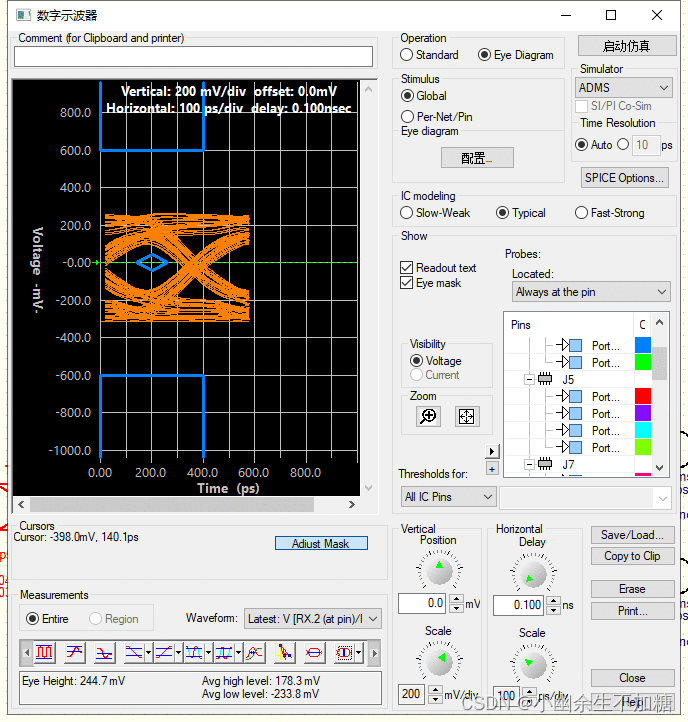

(8)测量眼宽和眼高,如图所示。

可以看到在差分网络中有很多没有耦合的部分,这部分代表了那些不得不绕过孔或者焊盘的线,不能保持很好的差分间隔。因为这一部分造成了阻抗不匹配,所以将使它们最小化。如果不得不使用它,那就使线长尽量短。

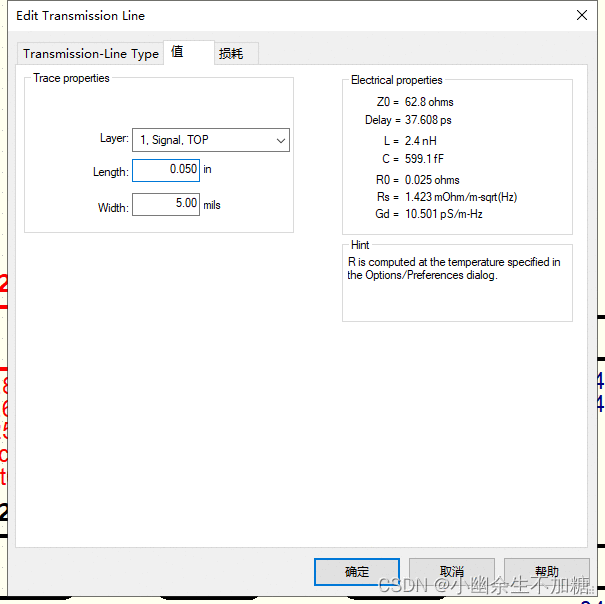

(9)在TX端放大,可以看到串联电容(J8和J9),如图所示。在网络中,看到有没有耦合的部分,现在减小它的长度来查看接收端的信号质量是否得到改善。

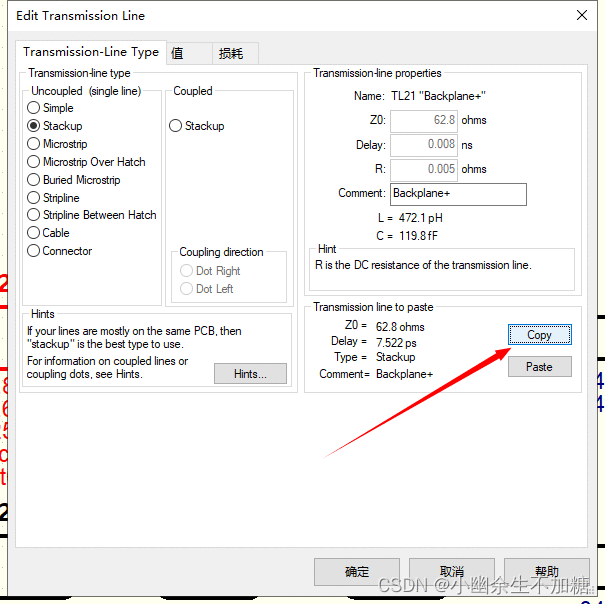

(10)双击TL21,选择“Values”选项卡,在长度栏中输入0.05,如图所示。

(11)选择“Transmission -Line Type”选项卡,单击“Copy”按钮,如图所示。

(12)单击“OK”按钮。

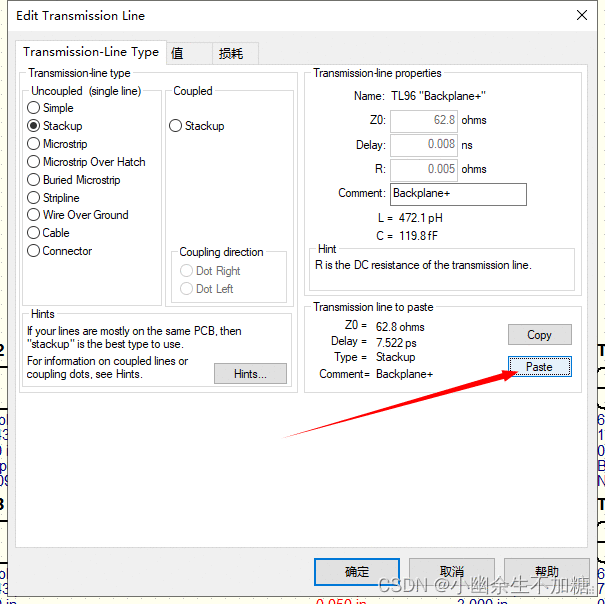

(13)接下来,将TL21的参数粘贴到TL22、TL91、TL92、TL78、TL79、TL95和TL96。

①双击想要改变的传输线,打开如图所示对话框。

②单击“Paste”按钮。

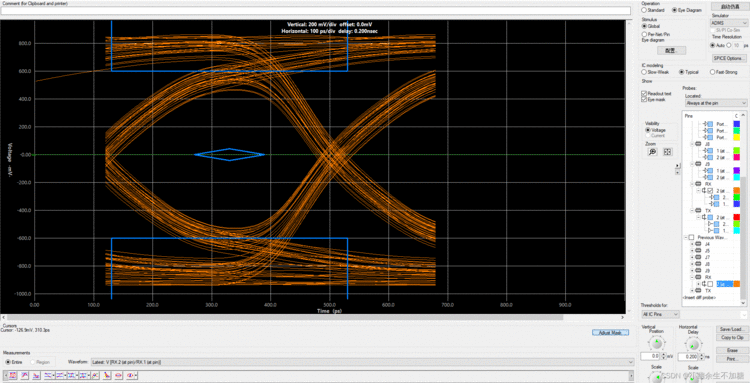

(14)打开示波器,单击“Start Simulation”按钮,仿真眼图如图所示。

(15)确保关闭之前仿真的眼图。

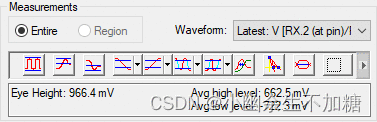

(16)测量眼宽和眼高,如图所示

(17)比较上述结果,发现眼宽和眼高已经得到改善。接下来,观察差分线之间长度的不同对接收端眼图的影响。

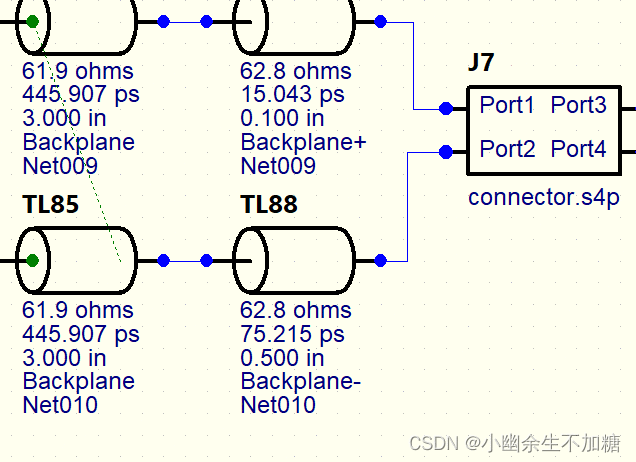

(18)在TL88处放大,如图所示,因为它的线长是500mil,与 400mil的差分线线长不匹配。

(19)设置长度为0.05in,如图所示。

因为TL97是0.1in,与50mil线长不匹配。

(20)改变TL71的线长为0.1in,因为它引起接插件上的长度不匹配

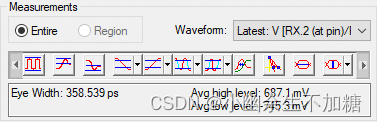

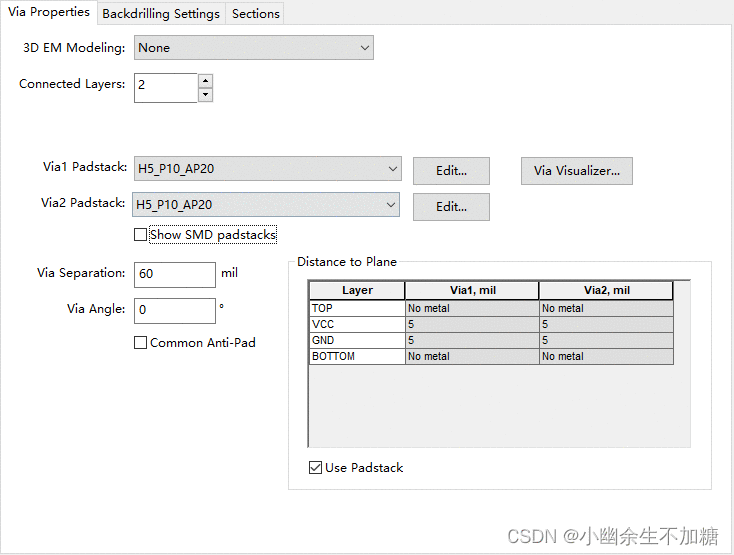

(21)再次仿真,结果如图所示。记录眼图参数

(22)可以看到,后者差分线长度匹配后眼图明显得到改善。接下来,观察过孔参数和过孔个数对通道的影响。

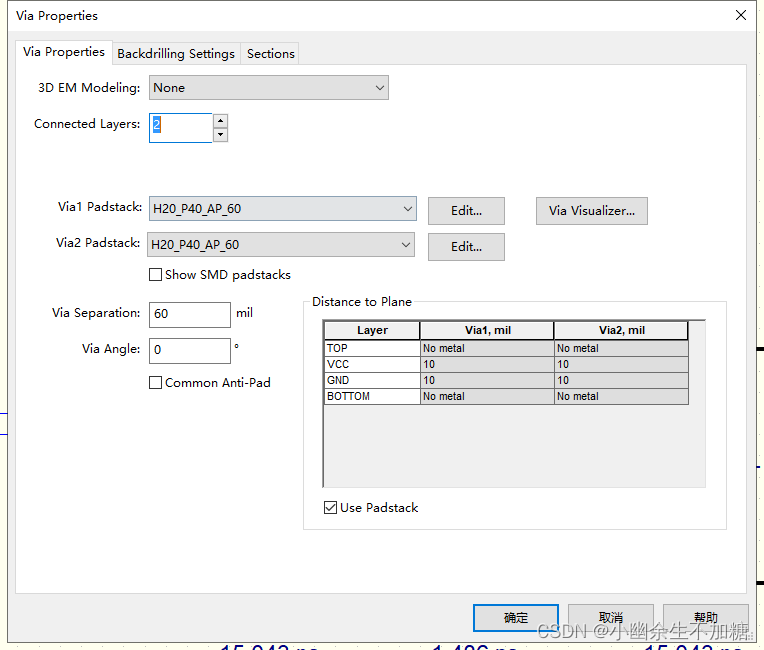

(23)双击过孔V3,单击“Edit”按钮,打开如图所示对话框。正如所看到的,过孔V3尺寸比较大,下面将使用尺寸较小的过孔来查看对接收端眼图的影响。

(24)在对话框中单击“Cancel”按钮。

(25)从已经分配的“Padstack”下拉列表中选择“H5_P10_AP20”过孔,如图所示。

(26)单击“Via Visualizer”按钮查看过孔的不同,如图所示。

(27)对V4和V2过孔重复(25)和(26)操作步骤。

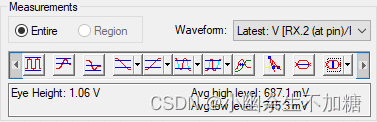

(28)再次仿真,结果如图所示。记录眼图参数所示。

(29)比较改变过孔前后的眼图发现,使用小的过孔并且将其距离拉大对眼图没有太大影响。

接下来,将增加通道的长度来查看对接收端眼图的影响。

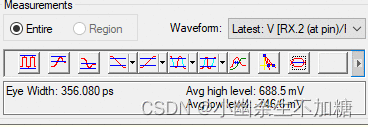

(30)双击TL80或者TL81,在耦合区域的长度部分输入40in,如图所示。

(31)再次仿真,结果如图。记录眼图参数,如图所示。

通过以上实验发现,两个眼图的眼宽和眼高都由于通道长度的增加而减小。

接下来,将使用加预加重的驱动模型来查看对接收端眼图的影响。

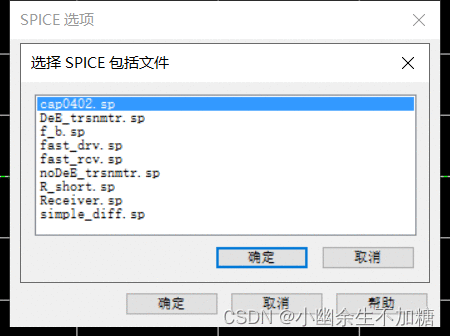

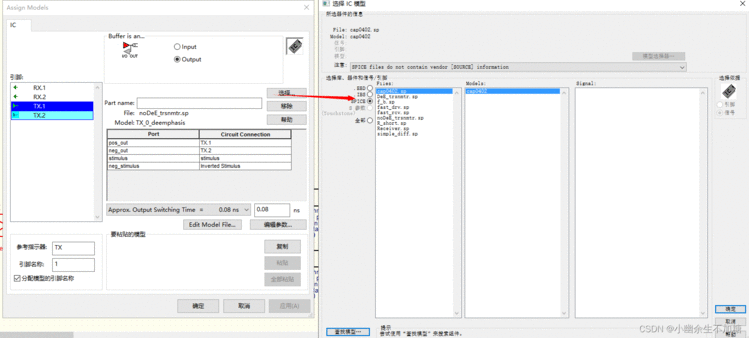

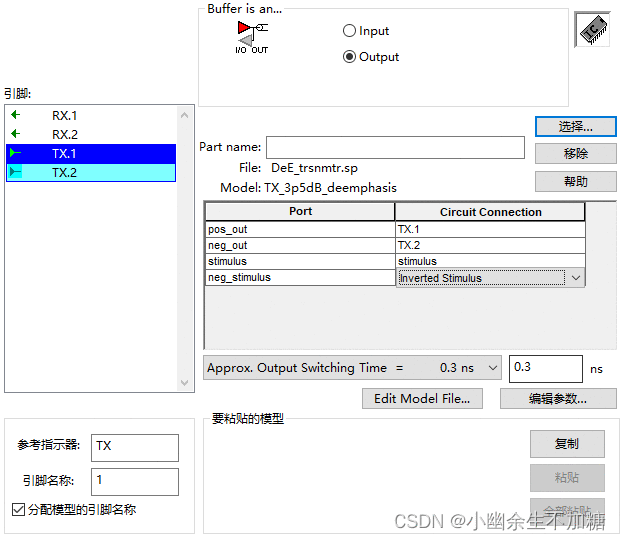

(32)分配 DeE_trsnmtr.sp模型给发射缓冲器。

①双击TX buffer 符号。

②单击“Select”按钮。

使能 SPICE 选项。

选择“DeE_trsnmtr.sp”,如图所示,单击“OK”按钮。

(33)在对话框中设置以下参数,如图所示。

pos_out:TX.1

neg_out:TX.2

stimulus: stimulus

neg_stimulus: Inverted_Stimulus

从下拉列表中设置激励参数,如图所示。

Approx Output Switching Time: 0.08ns

Stimulus V high:1V

Stimulus Vlow:-1V

(34)单击“OK”按钮

(35)再次仿真,结果如图所示。记录眼图的测量参数。

(36)比较前两次的仿真结果可以发现,预加重很大程度上改善了传输线上接收端的眼图。

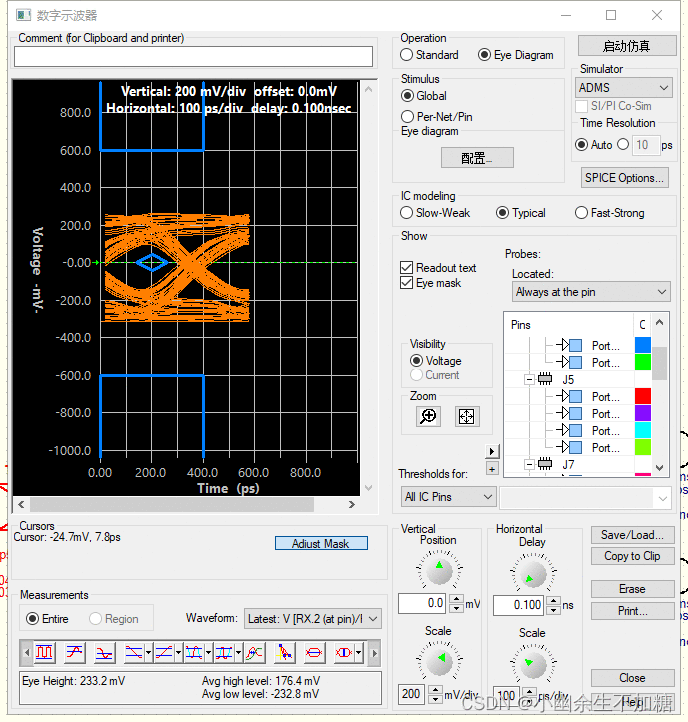

(37)如果时间允许,给激励添加10%的抖动,再次进行仿真,结果如图,眼图参数测量如图所示。

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有