作者:哭泣的玫瑰花丶_443 | 来源:互联网 | 2024-11-13 20:33

本文详细探讨了电平触发和边沿触发的基本原理及其在CMOS电路中的应用,包括普通触发、D触发器、带异步置位和复位端的触发器等。通过对比两种触发方式,帮助读者更好地理解它们的区别和应用场景。

在数字电子学中,触发器是一种重要的时序逻辑元件,用于存储数据和控制信号。触发器和锁存器的主要区别在于触发器增加了时钟信号(CLOCK,简称CLK)的输入端,只有在时钟信号到来时,触发器才能根据输入信号改变状态。

电平触发

普通电平触发

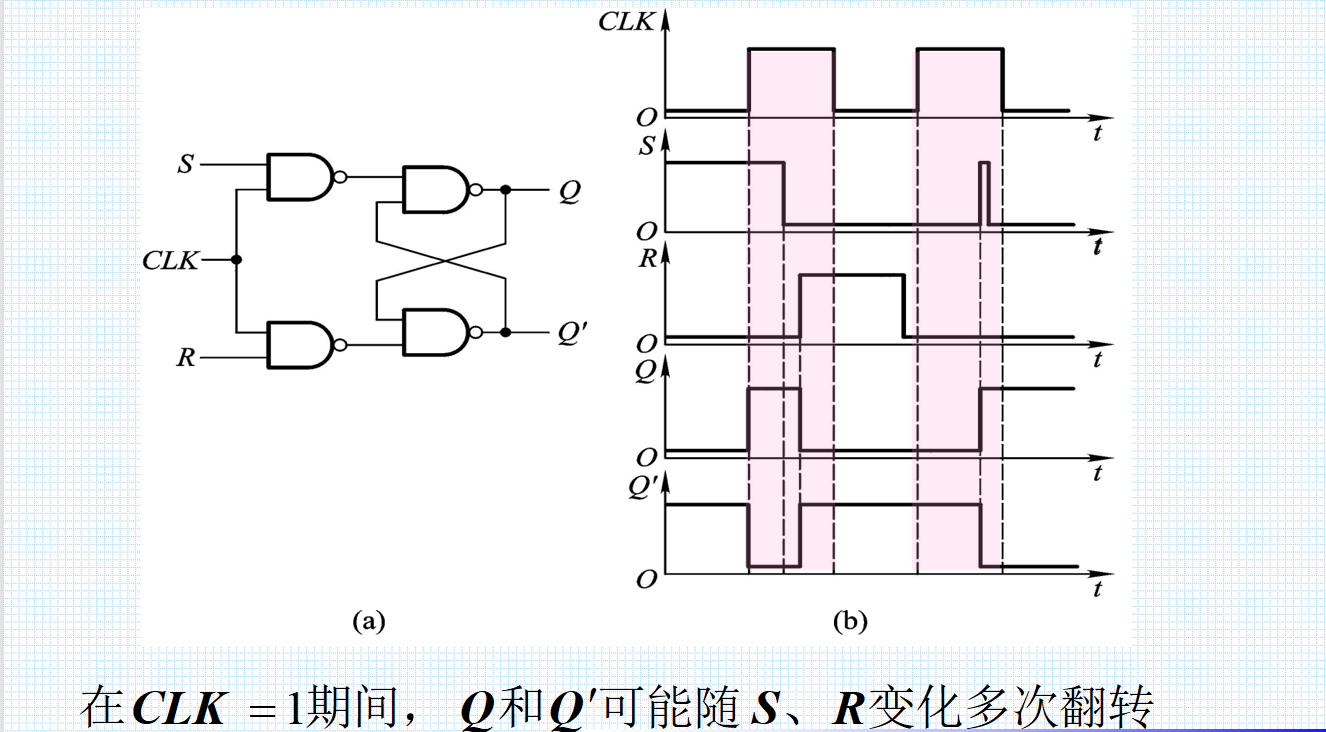

在电平触发模式下,当CLK信号变为有效电平时,触发器才能接受输入信号,并按输入信号将触发器置为相应的状态。在整个CLK有效电平期间,输入信号的变化都会导致触发器输出状态的改变。这种机制容易导致输出状态的不稳定,特别是在输入信号频繁变化的情况下。

例如,在CLK为高电平(1)时,如果输入信号S和R多次变化,输出状态Q也会随之多次翻转,从而引发不稳定现象。

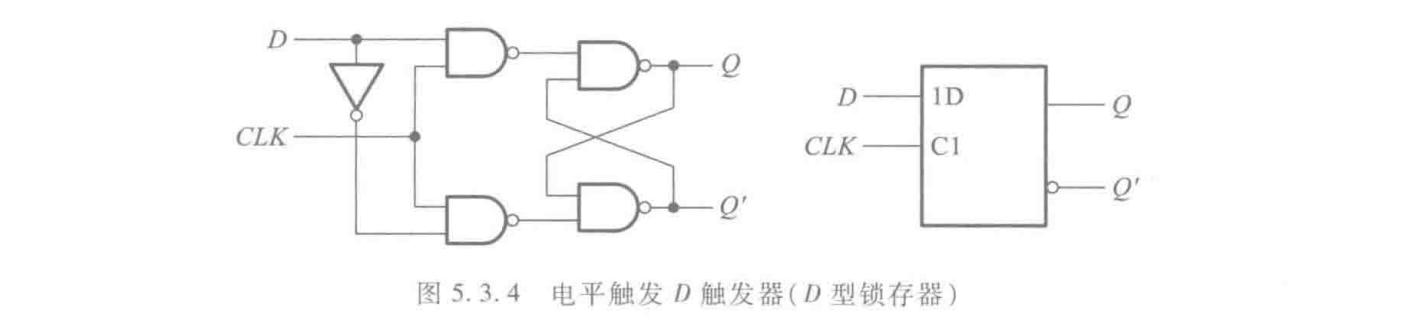

D触发器

D触发器是为了适应单端输入信号的需求而设计的。通过将电路改接成特定形式,D触发器能够解决触发器状态不确定的问题。具体来说,只要确保R和S不同时为1,触发器就不会出现状态不稳定的情况。最简单的方法是令S = /R,此时仅将S作为输入端(用D表示),即可得到D触发器。

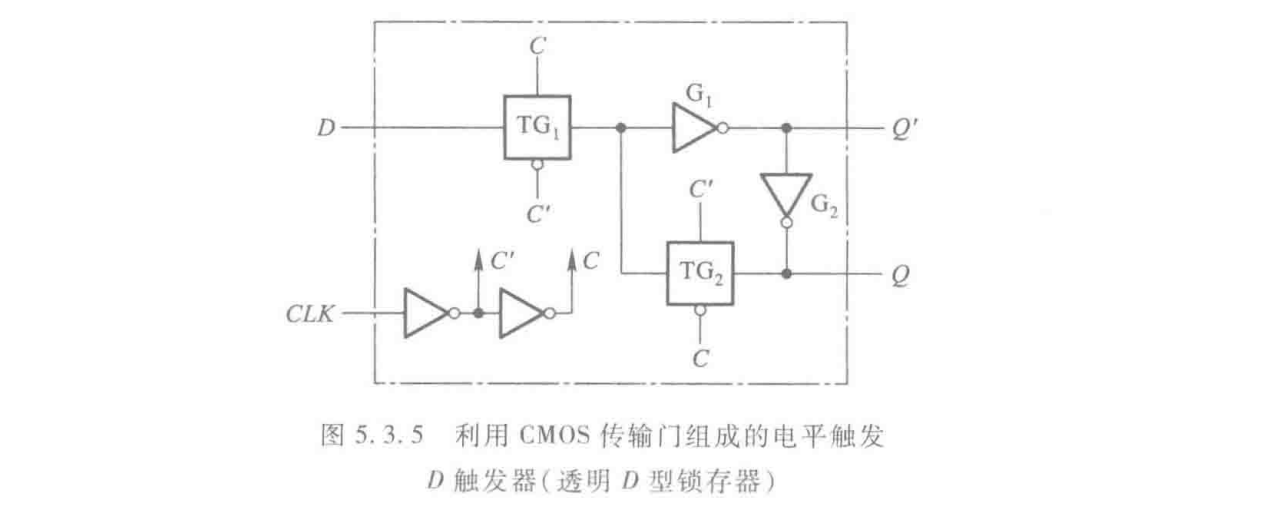

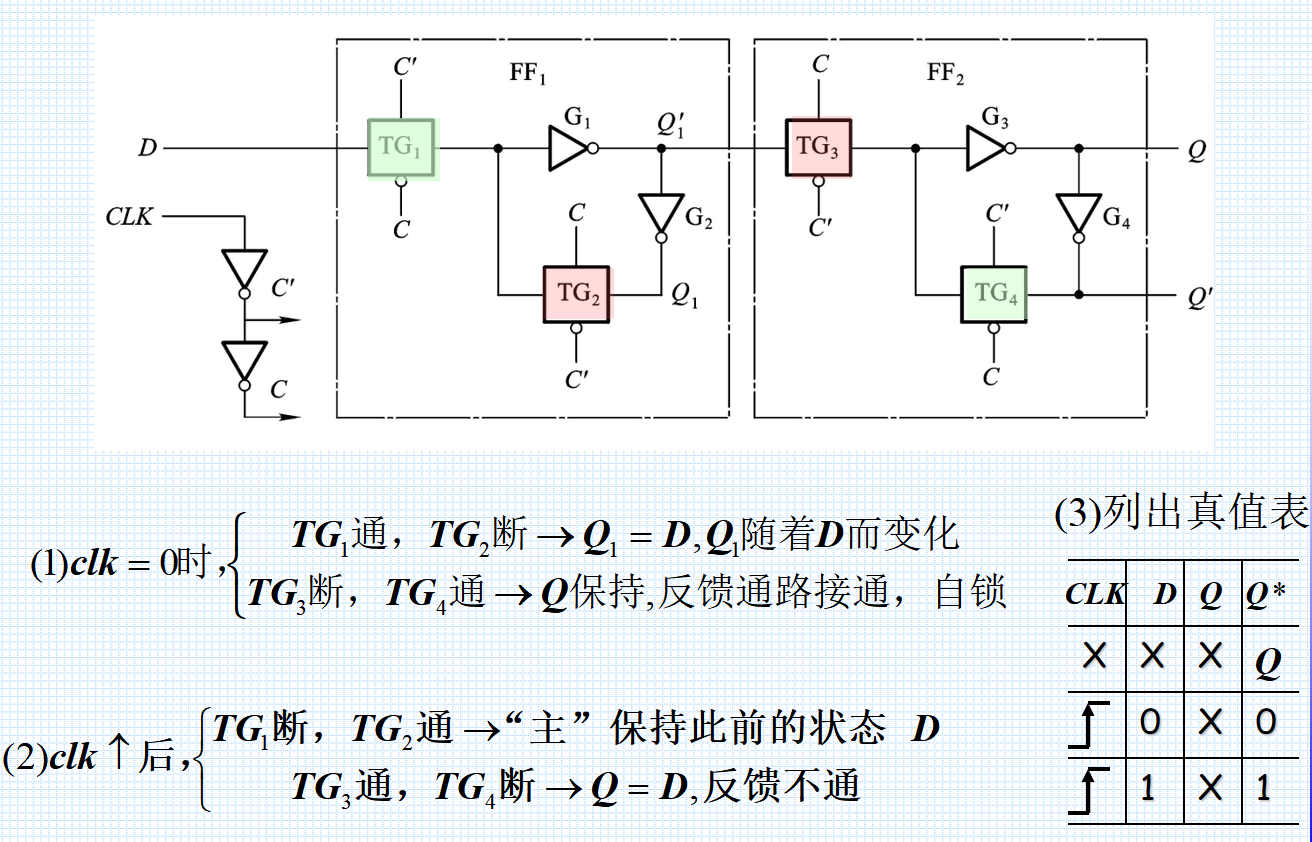

CMOS传输门组成的低电平触发

在CMOS电路中,经常利用CMOS传输门组成电平触发触发器。当CLK = 1时,传输门TG1导通,TG2截止,Q = D。在整个CLK为1的时间段内,Q端的状态始终跟随D端的状态变化。当CLK回到0后,TG2导通,TG1截止。由于反相器G1输入电容的存储效应,短时间内G1输入端仍保持为TG1截止前的状态,且此时反相器G1、G2和传输门TG2形成了状态自锁的闭合回路,因此Q和Q'的状态被保存下来。

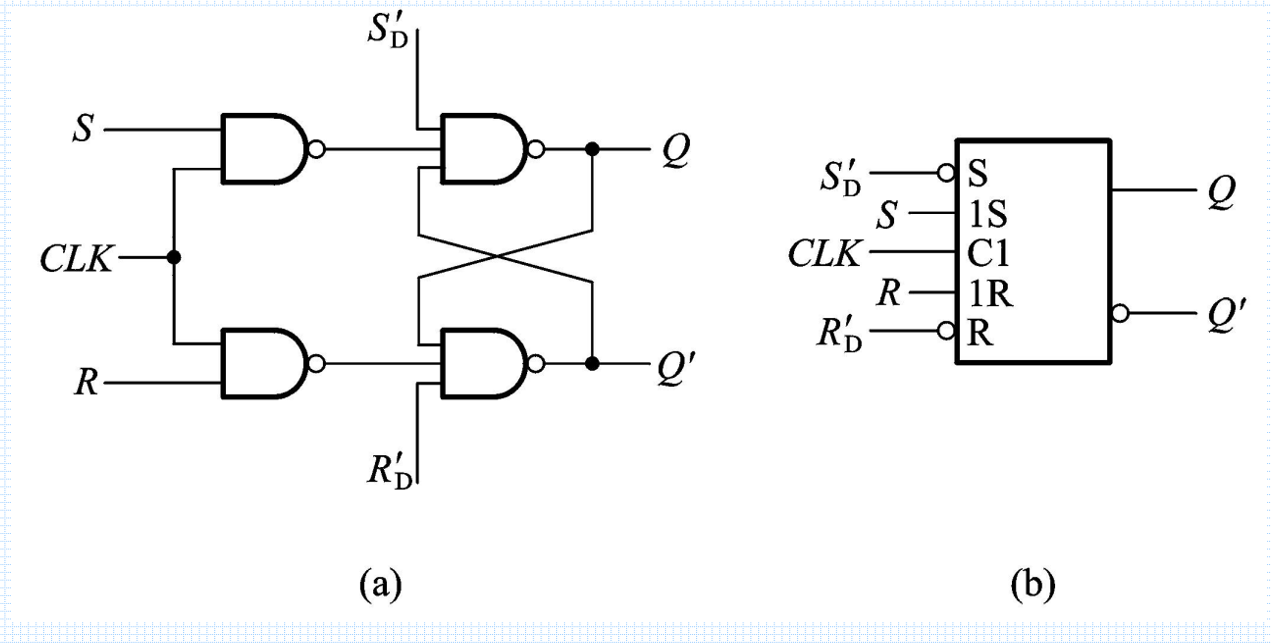

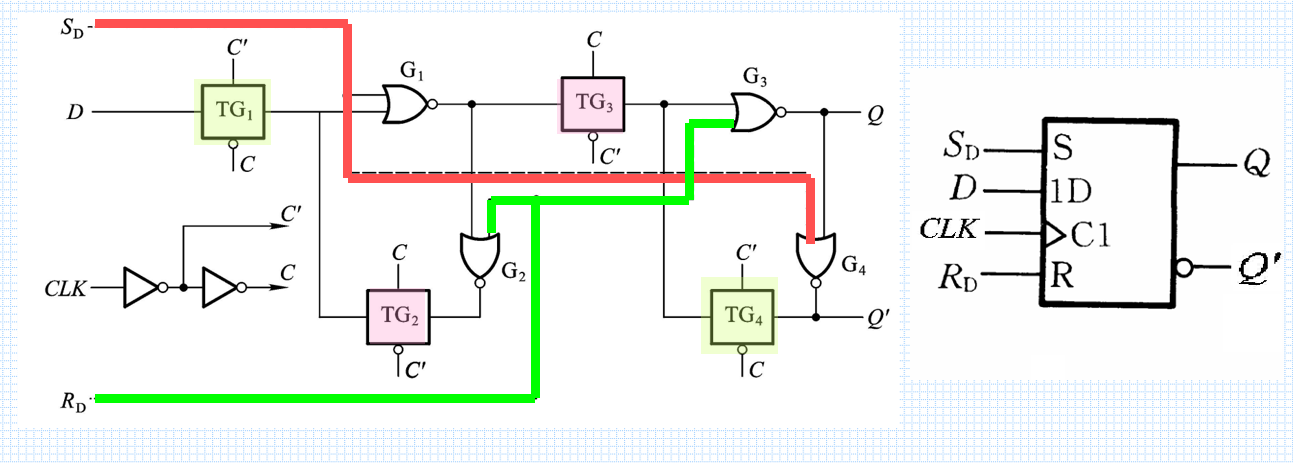

带异步置位、复位端的电平触发

在某些应用场合,需要在CLK有效电平到来之前预先将触发器置成指定状态。通过在SD和RD端加入低电平信号,可以立即置位或复位触发器,不受时钟信号的限制。在时钟信号下正常工作时,应将SD和RD端置于高电平。

边沿触发

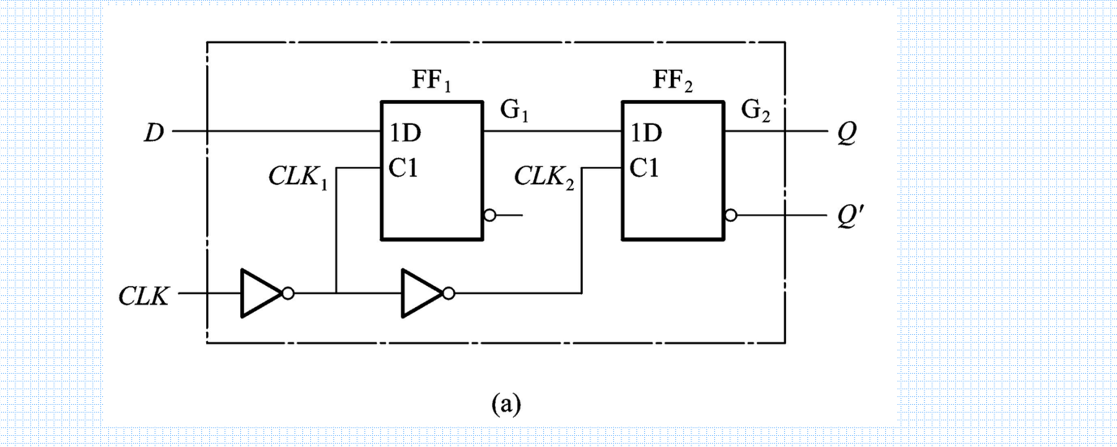

为了提高可靠性和抗干扰能力,希望触发器的次态仅取决于CLK的下降沿(或上升沿)到来时的输入信号状态,与此前后的输入状态无关。通常使用两个电平触发D触发器组成的边沿触发器来实现这一目标。

CMOS中的边沿触发器

在CMOS电路中,边沿触发器的工作原理与电平触发中的CMOS边沿触发分析类似,只是多了一个触发器。具体来说,当CLK为低电平时,只有主锁存器有效,G1会随着D变化,但输出G2始终不变。当CLK为高电平时,只有从锁存器有效,G2会随着G1变化,但此时主锁存器处于保持状态,G1不变,因此G2也保持不变。只有在时钟上升沿时,G1还在跟随D的值,而G2正要开始跟随G1的值,此时D的值可以通过G1传递到输出G2,D触发器输出改变。

带异步置位、复位端的边沿触发

类似于电平触发,边沿触发器也可以带有异步置位和复位端。通过在SD和RD端加入高电平信号,可以立即置位或复位触发器,不受时钟信号的限制。

电平触发和边沿触发的区别

电平触发是在高或低电平保持的时间内触发,而边沿触发是在高到低或低到高的瞬间触发。具体来说,边沿触发在数字电平变化的电压上升沿或下降沿达到一定阈值时产生触发,而电平触发在电压达到高或低电平一段时间后(通常是最小脉冲宽度的三分之一)才产生触发。

边沿触发通常时间较短,一般在微秒级别,响应速度快;而电平触发只需满足高或低电平即可,没有时间要求,适用于长时间低电平的情况。例如,中断计时或计数最好使用边沿触发,因为电平触发可能会导致较大的误差。电平触发一般用于简单的报警或开关类应用,时间要求不高。

边沿触发和电平触发的基本区别在于触发器和锁存器的不同。触发器是边沿触发,只有在时钟上升(或下降)的一瞬间,触发器会读取并锁存输入信号,输出信号仅在时钟信号上升(或下降)的一瞬间发生变化。而锁存器是电平触发,只要使能(enable)信号处于高电平(或低电平),输出就会随着输入信号变化,直到使能信号变为低电平(或高电平)时,输出才会锁存,不再随输入变化。