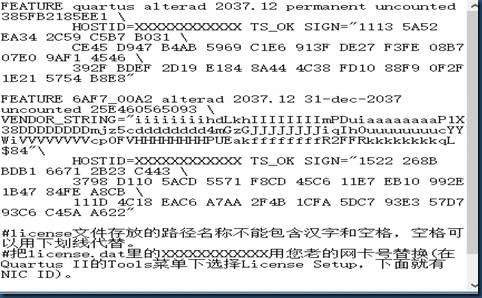

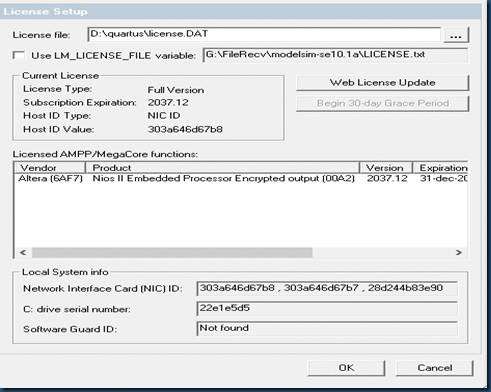

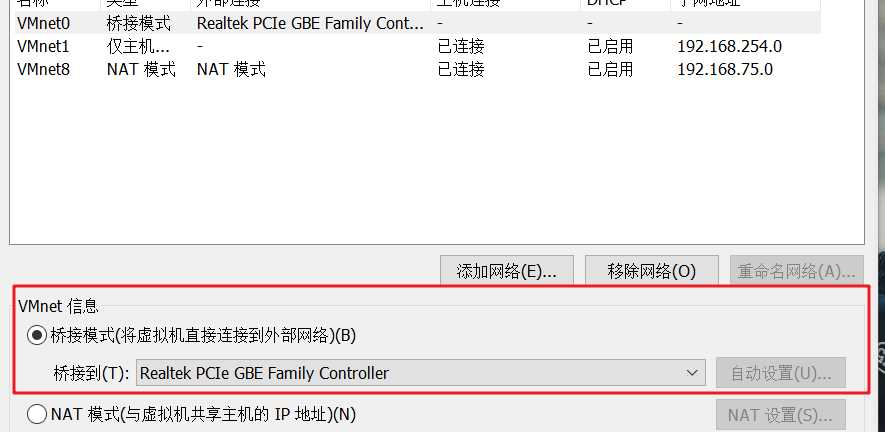

由于在意大利期间,用的xilinx公司的ZYBO板子,相应的软件用ISE,SDK。回国买了altera公司的板子,自然也要学习国内较流行的软件(TB大西瓜家,因此相关例程也是大部分引用他家)。Quartus 9.1软件下载后,安装是还挺顺利。我是windows8.1系统,破解是费了一些力气。首先下载Quartus_II_9.0破解器.exe,运行解压缩,找到sys_cpt.dll,根据电脑的位数,假设你本是32位,却安装了64位,软件会提示打不开有错误,所以其实若不清楚自己电脑的位数,可以试试的。将它放在Quartus安装路径下的bin文件下,路径为(D:\quartus\bin);打开Quartus软件,选择Tools工具栏下License Setup,查看地步Network Interface Card(NIC) ID,我的电脑上有三个地址,选择第一个就好了,把它复制代替License.dat里面的XXXXXX,例程里面说要把小写字母改为大写字母,最好把下边的一大串中文删除,我自己没有受到这方面的影响,替换后将License.dat保存,保存路径可以任选,依然是查看NIC ID的窗口,将License.dat加载进去,之后大概如下图,就破解成功了:)

以半加器为例,半加器(Half adder)电路指的是对两个数据位相加,输出一个结果位为和进位。

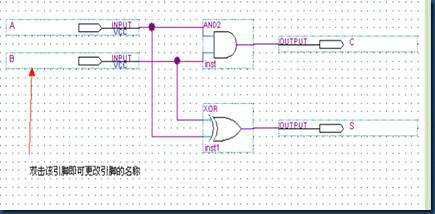

数据输入a0被加数,数据输入b0加数,结果位s0,进位c1,其对应的真值表和逻辑电路图如下:

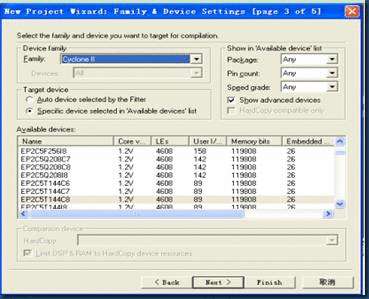

Altera 的 Cyclone® II FPGA 系列是低成本 90-nm 解决方案,它前所未有地提高了设计灵活

性,实现了高性能系统集成,关于它的特性,在综合仿真时,打算慢慢记载。以半加器为例,用该系列的EP2C5T144C8完成仿真综合。

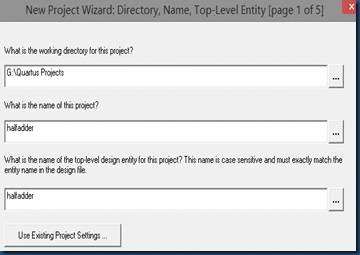

1.创建工程:打开Quartus软件,创建halfadder project,之后第二页(File name什么的)保持不动就好,next,选择相应的器件,之后仍旧保持不动(此页面保持各个为None),依旧next,最后一页finishi.

2.图形输入:用QuartusII原理图输入设计法进行数字系统设计时,不需要硬件描叙语言,利用数字逻辑电路基本知识的基础上,利用软件提供的EDA(Electronic Design Automation)平台设计数字电路或系统。

2.1 选择File-New,选择 Block Diagram/Schemetic File打开图形编辑窗口,在图形中双击,弹出的对话框中,输入半加器所用的器件(异或门xor;二元与门and2;输入input;输出output);鼠标点击input,output,选择properties,输入A,B,C,S.

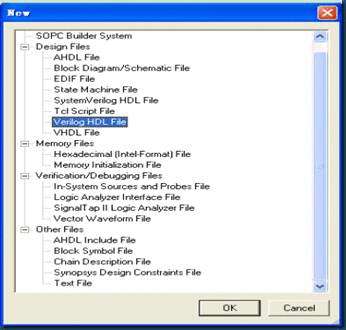

2.2文本输入方式:Quartus Ⅱ自带文本编辑器,用于程序设计输入。与图形输入类似,选择 Verilog HDL File 输入方式,即可打开文本编辑器

3.功能仿真:验证设计时序是否符合要求:工具有modelsim,Activehdl,NC-verilog/Vhdl,各厂家自带工具。

3.1.选择【File】--【New】选项,打开新建文件类型选择窗口

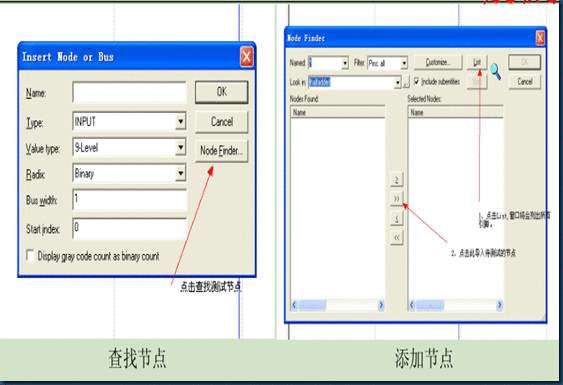

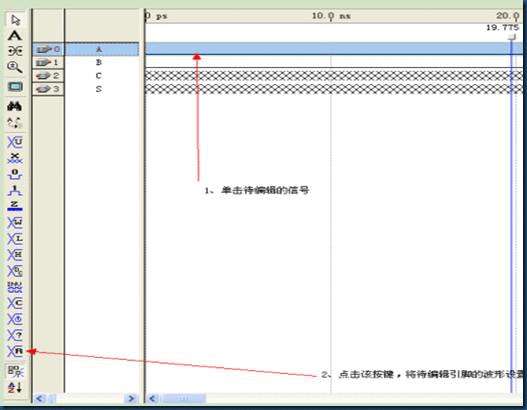

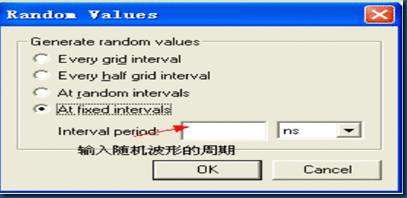

3.2.选择 Vector Waveform File(矢量波形文件) 打开波形仿真窗口,双击空白处,出现对话框(该对话框用来查找节点(Node Finder),加入节点(点击list),加入完成后OK,出现波形)。在波形左侧工具栏点击,带R标志,设置随机波形的周期,输入10,在ns前。

3.3.添加仿真测试信号,设置输入信号和仿真参数设置

京公网安备 11010802041100号

京公网安备 11010802041100号