ddr2 工作时序与原理

2014年05月02日 15:12:08 Chen_Eric 阅读数:4072

1.4-bit Prefetch

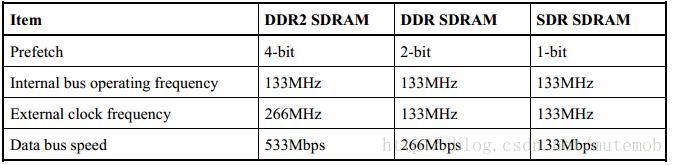

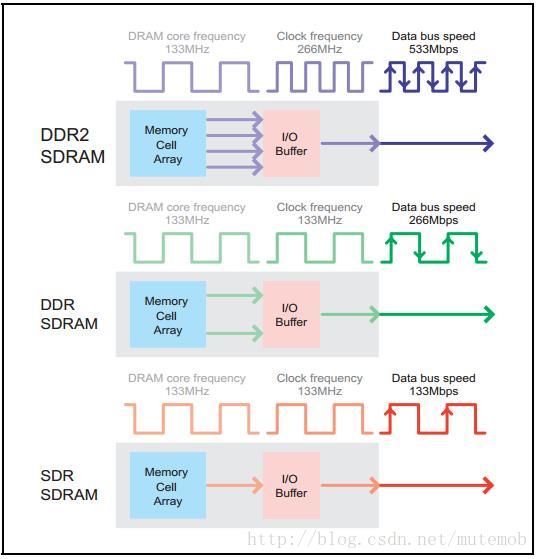

直接上一个表,看看DDR2的三个频率的关系,下图是内部时钟均为133MHz的DDR2/DDR/SDRAM的比较,由图可以看到,相比于DDR,DDR2由于是4-bit Prefetch,外部时钟是内部总线时钟的2倍,而DDR和SDRAM中,这两个时钟频率相等

上一个对比图,看的会更清楚一点儿:

在 SDRAM 与 DDR 时代,这两个时钟频率是相同的,但在 DDR-Ⅱ内存中,内部时钟变成了外部时钟的一半。以 DDR-Ⅱ 533 为例,数据传输频率为 533MHz( 对于每个数据引脚,则是 533Mbps/pin),外部时钟频率为 266MHz,内部时钟频率为 133MHz。因为内部一次传输的数据就可供外部接口传输 4 次,虽然以 DDR 方式传输,但数据传输频率的基准— — 外部时钟频率仍要是内部时钟的两倍才行。

2. DDR-Ⅱ的新操作与新时序设计

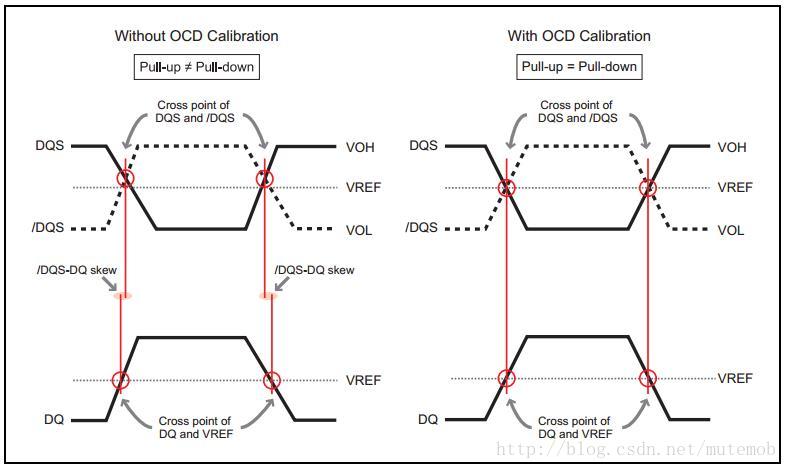

2.1片外驱动调校(OCD,Off-Chip Driver)

DDR-Ⅱ内存在开机时也会有初始化过程,同时在 EMRS 中加入了新设置选项,由于大同小异,在此就不多说了。在 EMRS 阶段,DDR-Ⅱ加入了可选的 OCD 功能。

OCD 的主要用意在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值。目的是让 DQS 与 DQ 数据信号之间的偏差降低到最小。调校期间,分别测试 DQS 高电平/DQ 高电平,与 DQS 低电平/DQ 高电平时的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出 OCD 操作。

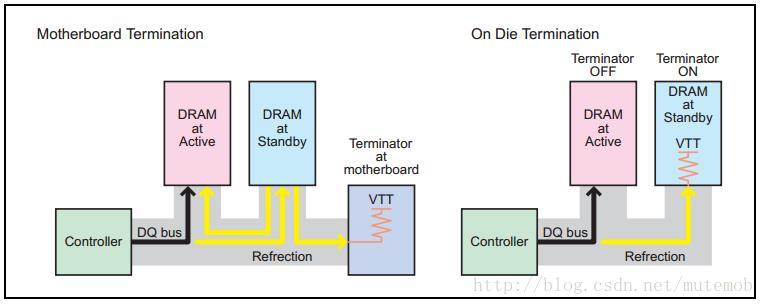

2.2 片内终结(ODT,On-Die Termination)

所谓的终结,就是让信号被电路的终端吸收掉,而不会在电路上形成反射,造成对后面信号的影响。

在 DDR 时代,控制与数据信号的终结在主板上完成,每块 DDR 主板在 DIMM 槽的旁边都会有一个终结电压岛的设计,它主要由一排终结电阻构成。长期以来,这个电压岛一直是 DDR 主板设计上的一个难点。而 ODT 的出现,则将这个难点消灭了。ODT 将终结电阻从主板上移植到了内存芯片内部,主板上不在有终结电路。ODT 的功能与禁止由内存控制器控制,ODT 所终结的信号包括 DQS、RDQS(为 8bit 位宽芯片增设的专用 DQS 读取信号,主要用来简化一个模组中同时使用 4 与 8bit 位宽芯片时的控制设计)、DQ、DM 等。

上图中,左边就是DDR时代,在主板上完成信号终结,右边就是从DDR2开始,在内存芯片内部终结信号。在内存芯片工作时系统会把终结电阻器屏蔽,而对于暂时不工作的内存芯片则打开终结电阻器以减少信号的反射。由此DDR2内存控制器可以通过ODT同时管理所有内存引脚的信号终结。并且阻抗值也可以有多种选择。如0Ω、50Ω、75Ω、150Ω等等。并且内存控制器可以根据系统内干扰信号的强度自动调整阻值的大小。

2.3前置 CAS、附加潜伏期与写入潜伏期

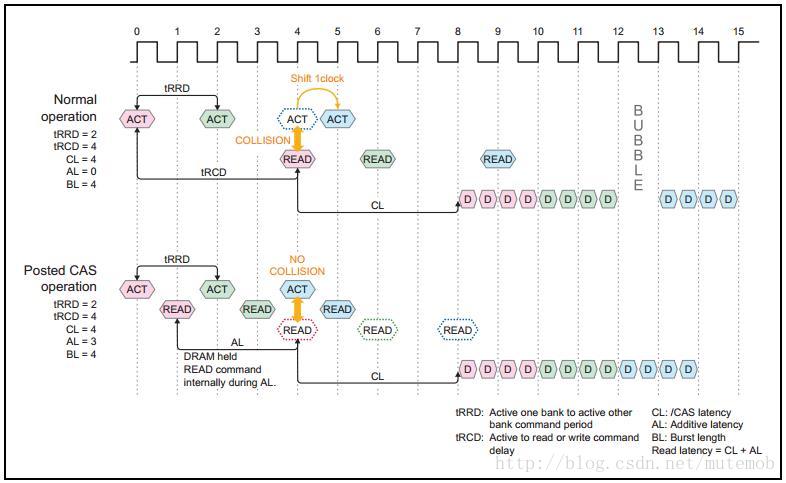

前置 CAS(Posted CAS)是为了解决 DDR 内存中指令冲突而设计的功能。它允许 CAS 信号紧随 RAS 发送,相对于以往的 DDR 等于将 CAS 前置了。

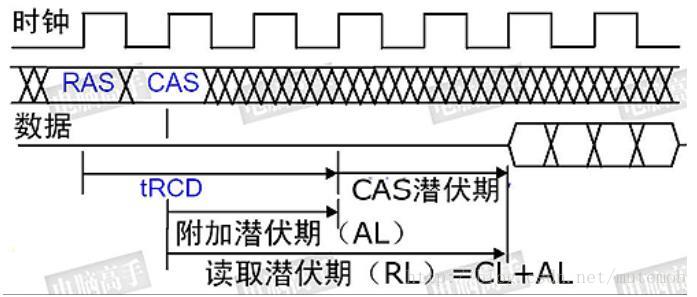

这样,地址线可以立刻空出来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生,但读/写操作并没有因此而提前,仍有要保证有足够的延迟/潜伏期,为此,DDR-Ⅱ引入了附加潜伏期的概念(AL,Additive Latency),与 CL 一样,单位为时钟周期数。AL+CL 被定义为读取潜伏期(RL,Read Latency),相应的,DDR-Ⅱ还对写入潜伏期(WL,Write Latency)制定了标准,WL是指从写入命令发出到第一笔数据输入的潜伏期,不要将它和 tDQSS 弄混了,后者是指 DQS 而不是数据。按规定,WL=RL-1,即 AL+CL-1。

上图中,ACT表示的是激活信号,在没有前置 CAS 功能时,对其他 L-Bank 的寻址操作可能会因当前行的 CAS 命令占用地址线而延后,并使数据 I/O 总线出现空闲(上图中的BUBBLE处),当使用前置 CAS 后,消除了命令冲突并使数据 I/O 总线的利率提高。

设置 Posted-CAS 后,必须附加潜伏期以保证应有延迟,此时读取潜伏期(RL)就等于 AL+CL,从中可以看出 AL 的值为 CL+tRCD-1。

至此,DDR2的来龙去脉全部分析完毕,现在可以开始打开芯片手册,开始分析源码了。