作者:卝軎亟_621 | 来源:互联网 | 2023-09-06 17:19

汽车安全关键领域的嵌入式系统开发需要多年的时间积累和数以亿计的资金投入,而安全作为重中之重,无疑是软件开发初期架构和设计的核心。车辆的行驶安全与手刹、尾灯等部件息息相关,这些部件不仅是由人和机械控制,更是由运行在多核复杂异构处理器上的嵌入式软件控制——它们控制着汽车驾驶及动力转向,并以几微秒的时间间隙给出控制信号。开发多核处理器的挑战往往在于软件的时序,软件时序不仅受软件运行和输入的影响,还会受到其他处理器核心上运行软件的影响。

本文将从多核时序分析入手,探讨汽车领域嵌入式软件安全问题的解决方案。

01.机动车检验标志电子化

“多核时序分析”英文全称为Multicore Timing Analysis(以下简称MTA),指多核处理器的软件时序分析。虽然在理论上,多核处理器惊人的计算能力能使嵌入式系统更加强大和高效,但其软件执行速度受运行在其他处理器核心上的软件影响的风险也陡然增加。总线、内存、缓存、设备、运行在其他处理器核心上的FPGA(Field Programmable Gate Array,现场可编程门阵列)和GPU(Graphics Processing Unit,图形处理器)等共享资源,而资源占用所造成的干扰则会导致软件可能需要更长的执行时间。

如何量化这种干扰的影响?当软件在多核平台上运行时,如何进行分析、测试并获得具体的数据,以证明安全关键的软件的执行时间处于可被接受的时限内?

巴塞罗那超级计算中心(Barcelona Supercomputing Center,以下简称BSC)、Rapita公司(Rapita Systems Ltd)、雷神技术公司(Raytheon Technologies Corporation,RTRC)和马瑞利公司(Marelli Europe,MAR)的专家们多年来一直在研究这些问题的答案。使用专业工具和自动化技术是解决这些问题的关键,但专业工具的使用存在一定要求与限制。

02.专业工具

支持时序分析的商用专业工具对于简单(单核)电子器件是有效的,但无法扩展以满足当前新出现的多核特定认证要求和建议。

1、静态时序分析解决方案面临着一堵“复杂的墙”:既不能有效对日益复杂的硬件进行建模,也不能有效处理异常复杂的软件功能结构和语法特征。

2、基于测量的解决方案在单核分析市场渗透率较高,但无法完全解决引入多核带来的问题。这些解决方案通常专注于由综合功能测试策略确定的测量场景,但缺乏基于硬件专业知识的测试方法——这种方法有助于为多核中运行的任务推导出可信的时序界限,并提供必要的支持信息和足够的可追溯性。

03.干扰的分析和量化

结构化测试方法使用软硬件专家提供的多核时序数据。BSC的一项专业技术(被称为多核微基准测试技术或MμBT)能够让系统设计人员通过创建额外的干扰场景来对多核处理器的不同部分进行压力测试,从而分析和量化基于多核应用程序的干扰程度。

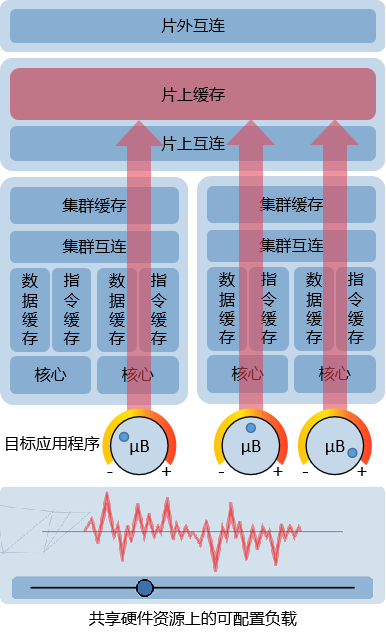

微基准测试(Micro-benchmarks)是基准测试中的一种方法,用来测试微小代码单元的性能。通常,这个微小代码单元可以是一段算法,一个方法或一个数据结构。微基准测试揭示了干扰通道对软件时序的影响,可以通过部署微基准测试对特定应用程序造成可配置和可量化的压力。微基准测试被专门设计用于展示单个明确定义的行为,并对特定硬件资源产生预期影响,同时尽可能防止在其他干扰通道上产生争用。微基准测试的主要功能包括:

1. 对特定的共享资源施加可量化的压力;

2. 其行为可通过事件监视器进行验证;

3. 捕获与时间相关的特定要求。例如,为控制争用而采取的缓解措施是否有效。

▲图1:微基准测试在干扰分析中的应用

04.测试设计方法

工程师可遵循标准软件V字形开发流程的七步设计及测试过程,从而更充分地了解软件在多核资源调用中受干扰的程度。

1. 多核处理器关键配置设置、干扰通道和事件监视器分析。硬件专家帮助确定关键配置的设置,建立框架,并在框架中确定干扰通道以及缓解措施。硬件事件监视器的识别也有助于为以下所有步骤提供验证方法。

2. 确定时序需求。开发人员需帮助最终用户识别系统的具体需求、时序要求、风险和系统安全问题。例如,验证任一硬件隔离方法的性能,以最大限度地减少干扰。

3. 测试用例设计。开发特定的测试用例以验证支持用户需求的假设集,包括定义在干扰通道分析中提供证据所需的MμBT项目。这涉及隔离执行(无干扰),根据微基准测试执行以评估应用程序的执行时间和硬件在不同可量化压力场景下的干扰敏感度。

4. 执行测试程序。该步骤可构建由测试框架、微基准和测量探头组成的测试程序,用来记录/跟踪结果。

5. 证据收集(测试)。测试程序在平台上执行以收集测试数据。

6. 结果分析。由技术专家审查测试结果,确认测试结果如何验证需求。

7. 验证结果并生成文档。对需求进行最终评审,生成文件和确认结果,以支持系统的安全性论证。客户可以直接使用完整的报告和分析工件来认证运行在多核上的软件。

▲图2:MTA验证步骤

图2所示的验证步骤旨在实现软件开发过程的可追溯性,并满足CAST-32A航空电子系统多核处理标准和ISO 26262《道路车辆功能安全》国际标准。

05.多核时序分析国产解决方案

想要详解软件多核时序行为中的干扰效应,既要了解多核体系结构的组件,又要了解软件中的调度和资源分配系统,对工程师的开发经验要求较高。

天目全数字实时仿真软件SkyEye,作为一款虚拟化技术仿真的专业工具,支持多核处理器仿真,可以通过硬件配置脚本为每个处理器核心创建包含有CPU独立资源(L1-Cache和寄存器)的模块。SkyEye采用统一的时钟调度机制来管理虚拟目标系统的时间,可以保证仿真的时序和真实目标系统是等比例的关系,确定性的时序状态和各处理器核心寄存器的实时状态监控可以帮助工程师进行多核时序的分析。处理器仿真时间和处理器寄存器监视如下图所示:

▲图3:处理器寄存器监视

另外,SkyEye还支持图形化构建目标系统,无需在意系统底层实现的细节。开发经验较少的工程师也能够快速上手并搭建复杂的硬件模型,进行软件的设计与开发。以P2020双核处理器目标系统搭建为例:

▲图4:P2020双核处理器搭建

工程师通过简单的拖拽便可快速搭建所需的虚拟目标系统,大大缩短产品研发周期,提高软件调试效率,解决多核时序分析的难题。

参考链接

https://www.embedded.com/ensuring-software-timing-behavior-in-critical-multicore-based-embedded-systems/