PDN是电源完整性中重要的角色之一。

对于了解PDN的工程师来说,PDN的设计轻而易举。而对于一知半解的人,PDN就像不可跨越的鸿沟,阻断了其技术晋升之道。

想必我们都听过,电容的重要作用之一就是去耦。

那么,在你的原理图设计和PCB设计过程中,你是如何设计去耦电容的呢?

当你摆放上一颗电容的时候,是否有想过,

为什么放置的是100nF而不是470nF?

为什么放置的是0201封装而不是0402封装?

为什么这个电容要摆放在这个位置?到底是横摆好还是竖摆好?

如果你从未考虑过以上3个问题,而你又想成为技术大咖,那么请喝口水,端坐,认真阅读接下来的硬知识。

PDN全称为power delivery network,翻译为中文为电源分配网络。仅从字面意思上,似乎很难理解这个概念。

我们换个角度来看。

网络可以干什么呢?想必很多人都知道,网络可以传送信息。而电源分配网络能干什么呢?自然而然,电源分配网络就是为了传送电流,输送功率。

所以,电源分配网络(PDN)就是将电源功率从电源输送给负载的实体路径。电流通过PDN从电源端流向负载端,再通过PDN,从负载端流回电源端。

假如拿电池,接两根线点亮1个灯泡。

那么正极和负极的两条线就叫PDN。

通过以上的例子,似乎PDN瞬间变得简单了,但如果真的这么简单,我们又何必大动干戈地去研究PDN呢?这就要研究理想与现实的差异了(又一个活生生的例子)。

在我们以前的学习过程中,都假设导线是理想模型,即:

无阻抗,(R0=0Ω),

无寄生电感(L0=0pH),

无寄生电容(C0=0pF)。

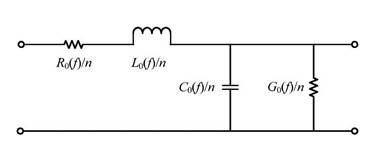

而实际生活中,任何金属都存在很低的阻抗和寄生电感,导线的实际模型如下:

所谓良好的导体实际是:

阻抗很低,(R0=8mΩ),

寄生电感很低(L0=8pH)

C0和G0则依赖于正极导线和负极导线的距离。一般C0极小,G0极大。

那么,原本简单的PDN,随着应用场景不同,也会出现相应的问题。以电池灯泡模型为例:

假如点亮灯泡需要至少5V的电压,1A的电流,在理想导线模型下,我们电池只需要输出5V即可。但实际情况下,由于正负极导线均存在8mΩ的阻抗,正负极导线会存在大约1Ax16mΩ=0.016V的压降,若想点亮灯泡,电池需要至少5.016V的电压。经过PDN的电流越大,压降越大,要求PDN的供电电压更高。

假如点亮灯泡需要的不是稳态电流,而是幅度1A,频率1GHz的交流电流,在理想导线模型下,无论频率怎么变化,电池都可以满足灯泡的需求。而实际情况下,由于正负极导线均存在8pH的寄生电感,导线上存在放入感抗X0=1GHz x 2π x 16pH=100mΩ。经过1A电流,压降为0.1V。所以需要电池供电电压至少为5.1V。频率越高,阻抗越大,压降也越大,要求的供电电压要更高。

可以看出,负载大小和负载频率的变化,最终都会导致PDN传输的负载的电压不再与电源输出相等,一旦负载获得的电压低于负载的工作需求,就会导致负载发生不可预见性的故障。

所以研究PDN的物理意义如下:

当负载稳态电流达到某个值时,PDN直流阻抗不得超过XXX(mΩ),来保证最大电流场景下,电源的供电电压满足负载的工作电压范围,这是PDN的低频部分。(Eg:我们经常会根据这个特性来计算PDN的目标值。假如某电源稳态输出为1V,最大电流为3A,要求输入电压波动不得小于5%(50mV),则目标阻抗Z0=16.6mΩ。故PDN直流阻抗务必小于16.6mΩ。)

当负载瞬态电流随着频率变化是,PDN上的寄生参数要足够小,来保证在某一频段范围内,PDN阻抗不得超过XXX(mΩ),来保证最大电流场景下,电源的供电电压满足负载的工作电压范围,这是PDN的高频部分。

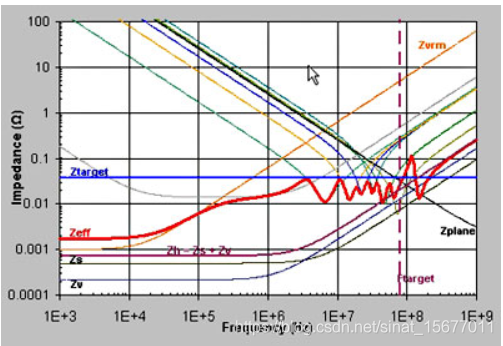

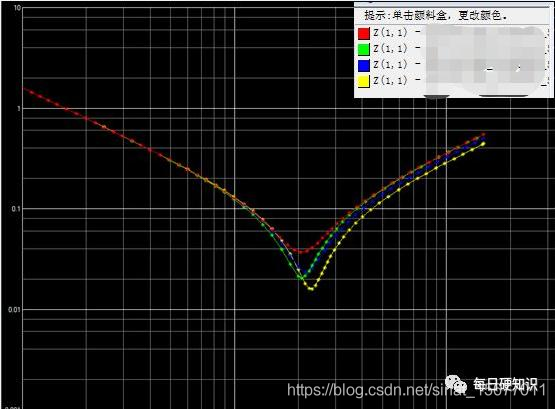

我们经常会看到PDN的仿真报告中,会给出如下形式的曲线:

纵坐标为阻抗,横坐标为频率。

通过PDN的物理意义,我们可以轻松看出:

该图要求频率从1KHz到1GHz之间,PDN阻抗要低于30mΩ以下。

实际PDN曲线在100MHz附近,大约300MHz以上时,PDN阻抗超标。其他频率范围,PDN满足要求。

现在我们通过简单的电池灯泡模型,理解了PDN的作用,PDN的物理意义以及PDN曲线读图。

之前用电池灯泡模型,为大家介绍了PDN的概念。电池灯泡模型是直流供电,负载很稳定(频率为0Hz),而且灯泡的负载特性几乎可以等效为电阻。所以电池灯泡模型,对PDN要求很低,拉两条线即可。

而如今随着集成电路工艺和PCB工艺的发展,硬件产品对PDN的要求也变得越来越高。究其原因,主要有如下3点:

随着现在处理器芯片的工作速度越来越高,内核电压也在逐渐降低。(数字逻辑1为高电平,同样的驱动能力,电压从0到1V需要的时间比电压从0到3V需要的时间短,需要的时间短,逻辑处理速度就高)。老处理器内核电压以3.3V为主,如今很多高端的处理器芯片内核电压为0.8V-1.3V之间,甚至更低。如果仍然按照0.8xVDD为逻辑1,0.2xVDD为逻辑0。老处理器逻辑1的电压范围为3.30.8=2.64V到3.31=3.3V,所以容许PDN上可以有660mV的压降。

新处理器逻辑1的电压范围为10.8=0.8V到11=1V,所以仅容许PDN上可以有200mV的压降。比老处理器的容限低了3倍。

根据欧姆定律,负载若消耗同样的电流,则新处理器的PDN阻抗就需要至少降低3倍。所以,处理器工作频率越高,对PDN要求更为严苛。

随着集成电路工艺的发展,芯片的集成度越来越高,高端的处理器内部继承了了成千上万亿个开关管,当这些开关同时打开或者关闭时,产生很大的瞬态电流。当这些开关管周期性交替打开关闭时,会产生各种频率的瞬态负载电流。这样的负载特性比电池灯泡模型远远复杂的多。所以更加要求PDN的直流阻抗要低,ESL要小。

PCB变得复杂了,一旦在布局布线过程中,考虑不慎则满盘皆输。

经验不足者,经常会遇到这样的情况,先走了关键信号,走完后发现信号贯穿了整个板子,导致电源和地平面不完整,去耦电容到芯片引脚的路径被打散,增加了寄生参数,造成PDN性能差。如果优化PDN,又导致布好的关键信号需要重新走线,增加了工作量。但事实上,大部分处理器芯片厂商在封装IC的时候,已经考虑了电源完整性和信号完整性,如果你的设计过程中,发现某关键信号导致PDN出了问题,那优先排查关键信号走线是否合适,大部分芯片在布局布线结束后,你会发现布线区域和电源平面区域,划分的井井有条,业界俗称走线顺。

综上,高速PCB使用的处理器有着很高的处理速度,很高的集成度,很复杂的功能。从而高速PCB对PDN的要求也更为严苛。在未来的硬件设计中,PDN的概念将和现在的欧姆定律一样,司空见惯。

把上面的问题反过来看,就能轻松总结出PDN对高速PCB电气性能影响是什么:

让我们在原理图设计,布局,布线之前,就能在脑海中勾勒出PDN蓝图。胸有成竹地设计出优良性能的PDN。

高速PCB上PDN由哪几部分组成?

以电池灯泡模型为例,可以轻松看出,PDN主要由电源(电池),和传输路径(导线)组成。

在高速PCB上,PDN同样由电源和传输路径组成。但在高速PCB上,电源和传输路径的形式有很多。

电源的形式有开关电源,LDO,电池,电容,电源-地平面对等。

传输路径有PCB走线,PCB过孔,芯片封装等。

将上述部分按照功能类型分类:

开关电源、LDO、电池这些可以成为电压调节模组(VRM),也就是我们俗称的电源。

电容按照此时的功能,称之为去耦电容。电源-地平面对的作用和去耦电容一样,但是由于其特殊性,将其单独列出。

PCB走线和PCB过孔,统一称为PCB。

芯片封装一般由器件厂家决定,我们改变不了它的特性,后续忽略不提。

所以,如果按照功能分类,高速PCB的PDN主要由如下几个模块组成:VRM、去耦电容、电源-地平面对、PCB组成。

但如果按照硬件设计流程的职能划分:

开关电源、LDO、电池、电容这些属于器件,在原理图设计阶段完成,我们称为原理图部分。

电源-地平面对、PCB走线,PCB过孔在布局布线阶段完成,我们称为EDA部分。

所以,如果按照硬件流程看,高速PCB的PDN从原理图设计到PCB设计的整个阶段都要考虑,二者缺一不可。

基于我们的研究都是硬货,所以我们按照功能来讲解PDN的重要组成部分:VRM、去耦电容、电源-地平面对、PCB。

毋庸置疑,是PDN中的C位,它为负载提供稳定的电流,为负载提供主要能量。目前用的最多的VRM应该是开关电源和LDO。

开关电源的主流拓扑有Buck和Boost,熟悉电源的伙伴们都知道,二者的结构中,都有个重要的器件—串联的功率电感。功率电感的存在是一把双刃剑,首先,它成就了开关电源,让开关电源在重载情况下,有很高的能量传输效率。但是,功率电感的存在也让开关电源不能提供高频负载电流。因为功率电感的感值一般在uH以上,所以1MHz以上的负载电流会在功率电感上呈现出很大的阻抗,使得开关电源无法为负载提供高频负载电流。

LDO相比开关电源,其频率相对较高,但LDO在负载较大时,损耗太大,不适合为大负载供电。

电池能提供相对较高频率的大电流,但是电池的电压会随着电量的耗尽而下降,电压不稳。

正是由于VRM的缺陷,去耦电容当仁不让地稳坐二哥位置。

我们知道高频负载由于频率高,对能量的获取都是瞬时的,所以每个周期抽取的电量很少。正是由于这个特性,电容就彰显出了重要的作用。从电容的公式我们知道:

C=Q/U,Q=I*t。

所以1uF的电容在电压为1V时,可以提供大约1A持续1us的电流。22uF的电容在电压为1V时,可以提供大约22A持续1us的电流.

1MHz的负载,周期也就是1us左右。

所以,去耦电容虽然存储的能量较少,但是为高频负载补充能量却显得绰绰有余。而且负载频率越高,容值越小的电容即可担此大任。

即使大哥和二哥为负载补充了全频段的能量,但是能否将能量尽可能多地传递给负载,就要看节奏位—PCB布局和布线了。

作为传输路径,我们在电池灯泡模型中就提到了:DCR小,ESL低。

所以EDA布局布线的原则简单粗暴:粗,大,短,直。

电源-地平面对就像和七仙女谈恋爱,可遇而不可求。

成本的压缩和走线的复杂程度,导致很难保证电源-地平面对是完整的。而如果说到电源-地平面对的作用,实际和去耦电容一样。只不过电源-地平面对是PCB本体搭建的电容。P电容的结构是金属中间夹层介质。而电源-平面对刚好保证了金属平面中间有一层介质。

由于VRM在为负载提供高频电流时,显得萎靡不振。所以去耦电容在PDN的地位等同于VRM。去耦电容存储存储的电荷虽少,但摆放合适的情况下,可以为负载提供所需要的高频电流。

去耦电容和滤波电容在本质上没有区别,它们都是电容,都是为了去除电源上的高频交流杂波。

滤波电容是滤除VRM自身产生的高频交流杂波(例如开关电源的纹波),常放置在电源的输出端,滤波电容将电源产生的交流杂波通过自身导入GND上,达到消除目的。

去耦电容是滤除负载自身产生的高频交流成分(例如开关噪声),常放置在负载的电源输入端。前面我们说过,负载突然抽取高频大电流,由于VRM萎靡,负载就只能靠PDN上的去耦电容来补充电流,一旦PDN不好,输入端的电源就会产生塌陷或者过冲,产生高频交流杂波。去耦电容是为负载补充高频的电流,来避免产生杂波。

正是因为此,工程测量噪声时,要求靠近输入电容测试,噪声是高频,示波器用全带宽。测量纹波时,要求靠近输出电容测试,纹波是低频。要求纹波用20M带宽。

所以,去耦电容为负载补充高频电流,防止负载产生杂波。滤波电容将电源产生的杂波短路到GND上,来消除杂波。这就是二者最大的差别。

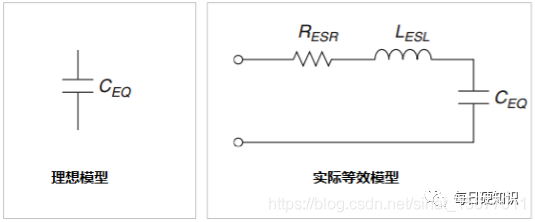

我们在物理学科中,知道电容的重要特性是“通交隔直”。这个词对电容的特性阐述的非常精准,但也因为光芒太亮,导致我们忽略了课本中的电容的另外1个特性:理想模型。

在理想模型下,负载的高频电流就是交流电流,而电容通交隔直,根据电容的阻抗公式Xc=1/2πfC。我们会以为,频率越高,电容的阻抗越小。所以忽略了理想模型的工程师,总是有个疑问:既然电容通交隔直,放的电容值越大,去耦效果岂不是越好?

理想的电容模型,电容就是1个简单的C组成,而实际电容的生产工艺中,由于存在金属连接,封装等各种因素,势必会引入寄生参数(主要为ESL和ESR,有些电解电容还存在漏电,就需要在电容模型边再并联个大电阻,此处忽略不计)。从而电容的理想模型和电容的实际模型如下:

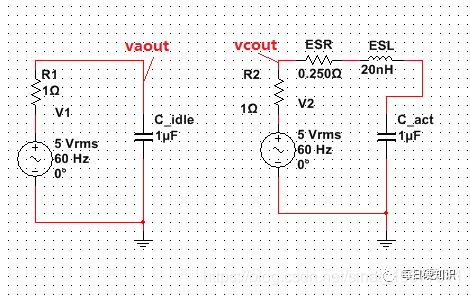

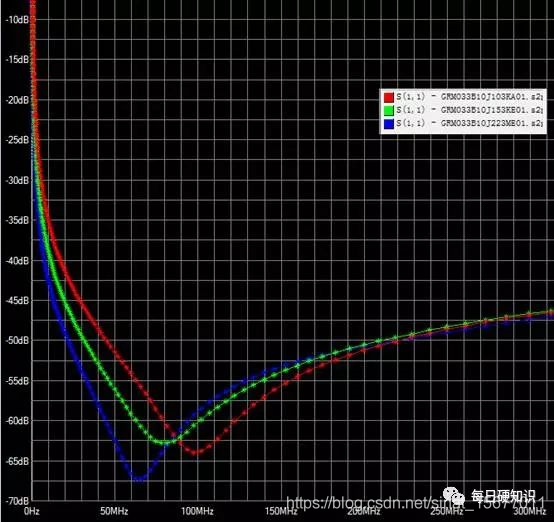

正式由于实际模型中出现了ESL和ESR,所以电容的阻抗公式Xc=ESR+1/2πfC+2πf*ESL。用仿真软件,进行仿真。

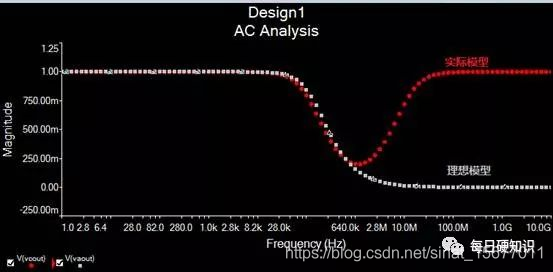

电容的频率响应曲线成了下面的这个样子:

我们看到:

理想模型,频率越高,电容容抗越小,直到趋近于0。

实际模型,在到达某个最低点后,随着频率越来越高,电容抗值又增加了。这就是理想与现实的差距。

在实际模型中,曲线最低点就是电容的谐振点,在谐振点处的频率称为电容的谐振频率,谐振点处的阻抗值为ESR。

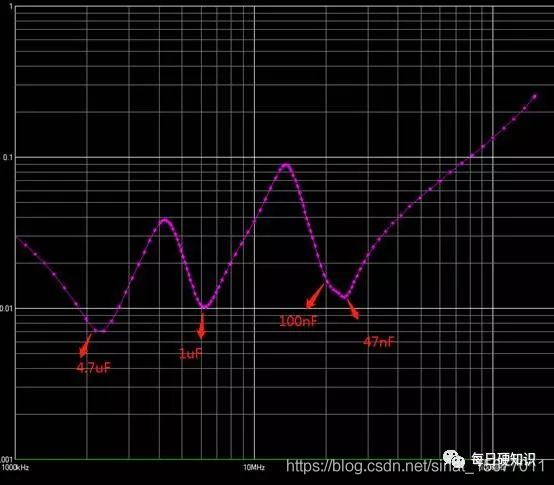

正是因为实际电容只有在频率谐振点处,阻抗最低,所以如果要实现PDN全频段阻抗都低,就需要搭配不同的电容来实现。

目前用的最广泛的是陶瓷贴片电容,陶瓷贴片电容主要有如下2个特性:

PCB的作用至关重要,就是将电源和去耦电容的电荷,尽可能无损耗的传输给负载,保证负载正常运行。PCB布局布线不合理会直接导致传输路径上ESR和ESL偏高,即使VRM性能优良,去耦电容性能强劲,PDN也会一塌糊涂。

所以我们在PCB布局布线时,需要:

尽可能地降低ESR,保证PDN在低频时满足阻抗要求。

尽可能地降低ESL,保证PDN在高频时满足阻抗要求。

布局布线对于ESR和ESL的影响基本是一致的:线越粗,越短,走的越直。ESR和ESL值越低。(传说中的粗短直理论)

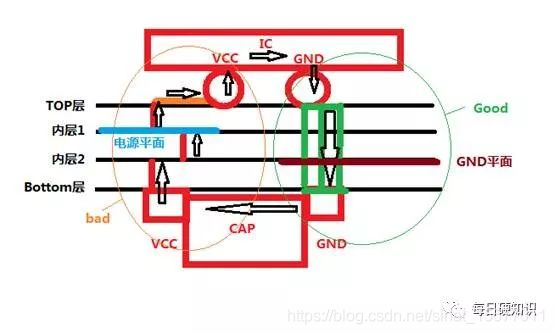

如下图,以双面布局为例,IC在TOP面,去耦电容在Bottom面。(这幅图中,传输路径VCC端,布局布线很差,传输路径的GND端,布局布线很好,用于做对比)

在设计前,首先明确电流的流向,明确电流通路,电源完整性有两个重要定理:A.电流总是走最短路径;B. 电流必须有返回路径。

去耦电容相当于为负载提供高频电流的电源,所以电流总是从电容的正极出发,经过PCB,给到负载正极,再通过负载的GND管脚流出,通过PCB,流回电容负极。

明确电流流向后,我们开始布局布线。

1.布局时靠近供电区域放置。按照走线越短原则,双面布局,势必要求电容的布局在IC相应供电pin脚的正下方,原本没有方向的电容,好像变得有方向了。电容的VCC端最好在IC的VCC正下方,电容的GND端最好在IC的GND端的正下方。如果IC的GND端正下方是电容的VDD端,那么PDN将大打折扣,环形电流路径上ESL越大(相当于绕线电感)。

2.基于电流流向,走线粗短直。如图,VCC经过3个不同的位置过孔,从Bottom分别经过4-3孔,3-2孔,2-1孔,到Top面,3个过孔垂直方向不在一条线上,ESL大。而GND从Top经过3个1-4孔,直接到bottom层,ESL和ESR就小。不同层的过孔尽量垂直于一条线上,即使无法保证垂直于1条线,每层孔与孔的位置不要太远。

3.基于电流流向,增加并联支路。基于电流流向,如果有过孔,可以增加过孔的数量。如GND路径,从Top打1-4孔,到Bottom。原本1个1-4过孔的寄生参数为6pH,打3个过孔,ESL就变成了2pH,降低了3倍,优化明显。

4.保证局部电源平面和局部地平面的完整性。可以在垂直于IC供电引脚的下方,建立VCC平面区域,在垂直于IC GND引脚的下方,建立GND平面区域。保证电容的电荷,从电容出发,经过走线和过孔,流到电源平面,在经过走线和过孔,给到负载。电流通过负载的GND管脚,通过走线和过孔,流回GND平面,再通过走线和过孔,流回电容GND端。如果电源的供电管脚存在多个,建立平面后,可以实现1颗电容为所有管脚去耦。

5.平面尽量靠近负载侧。如4层板,负载在1层,那平面优先考虑1层和2层。若6层板,负载在1层,平面优先考虑2层,3层。

以上原则,对单面布局同样适用,单面布局的难点仍然是平面能否保持完整?在PCB分层时,一定要仔细推敲,避免平面被信号打散。

转自------《每日硬知识》公众号

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有

京公网安备 11010802041100号 | 京ICP备19059560号-4 | PHP1.CN 第一PHP社区 版权所有