作者:书友68570125 | 来源:互联网 | 2023-05-19 18:29

插损验证

仅仅依靠叠层仿真无法完全保证插损满足要求,推荐使用频域方法测量PCB上的高频信号损耗和传播,任何设计的改变都需要重新评估插损是否依然满足要求。

对于带状线,如果在结构相同(完全相同的铜箔、材料和尺寸)的层上有相同阻抗的走线,则只需测量一个具有代表性的阻抗/层组合即可确保满足插入损耗要求。

减小过孔影响的方法:

通过从电路板的适当一侧探测(从顶部用于电路板下半部分的迹线,反之亦然)减小过孔残桩的长度,或者背钻。

环境影响插损

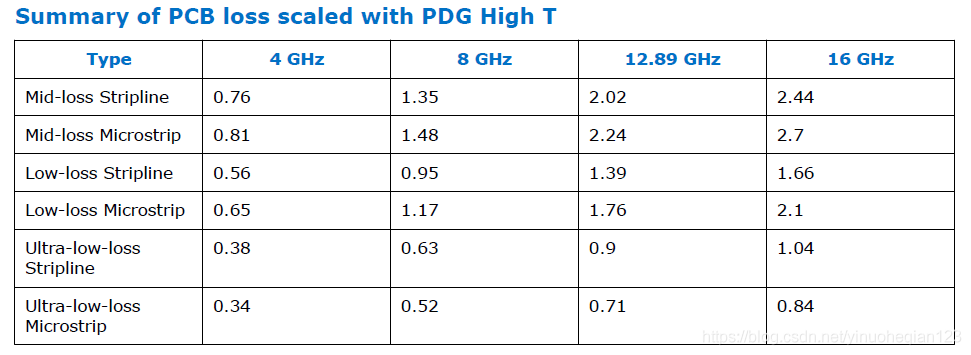

高速信号的高温模型(考虑到环境影响)假定不同的温度影响不同类型的PCB材料:

对于mid-loss材料增加16%

对于low-loss材料增加11%

对于ultra-low-loss材料增加8%

以上数据假设CPU区域温度为80°C,其他区域60°C。

在某些条件下,如果走线区域温度超过90°C,则需要额外的guard band,而且损耗考虑:

mid-loss增加26%,low-loss增加17%,ultra-low-loss增加13%。

注意,每种板材温度对插损的影响不同,需要提前和材料厂商或者板厂确认,并仿真验证是否有设计风险。

更小的过孔尺寸和更小的背钻残桩提高了CAF(conductive anodic filament)(可以简单理解为玻璃纤漏电)和过孔失败的风险,CAF风险主要的来源是pitch减小以及两个过孔之间的breakout差分走线导致的背钻到金属的距离过小。过孔失败主要的原因是8mil的孔尺寸,导致更高的纵横比。树脂塞孔会降低CAF失败。