本文转载自https://blog.csdn.net/qlexcel/article/details/79524504

PCB布线中为了满足差分的需求需要布等长线,为了满足高速时序的需求需要布蛇形线,下面以布SDRAM的地址线为例来说一下布蛇形线的过程,等长线同理。

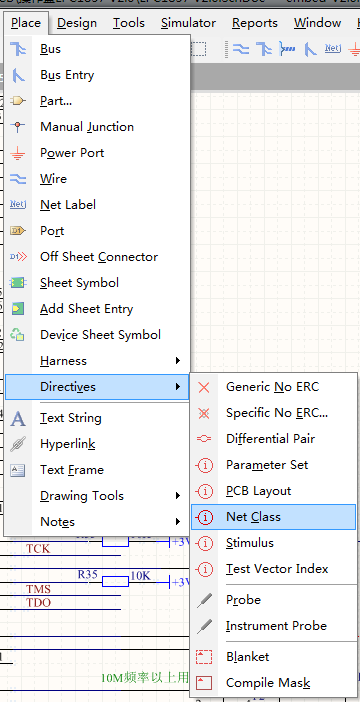

1、首先要为所有要画等长线的网络,放置上类

类的属性,按Tab键进行设置。名字无所谓,只要“Value”相同就行。

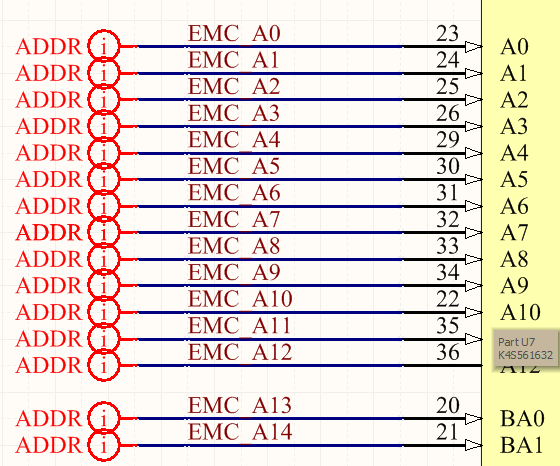

下面是要画等长线的网络,都放置上类的样子:

2、然后进入PCB,把所有的ADDR线都按正常的方式布完。

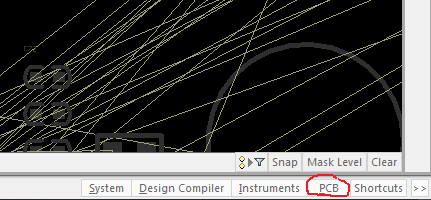

3、在AD的右下角打开PCB面板。

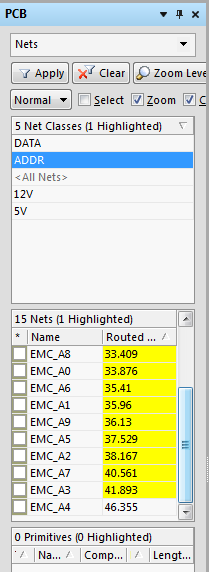

点开刚刚的ADDR类,可以看到ADDR类中的所有网络的布线长度。他们是按长度由小到大排列的。选择类中最长的那根线作为目标长度,我们这里的目标长度是46.355mm。(布蛇形线就是把所有的线的长度调整到一致,因此把短的线蛇形化变长)

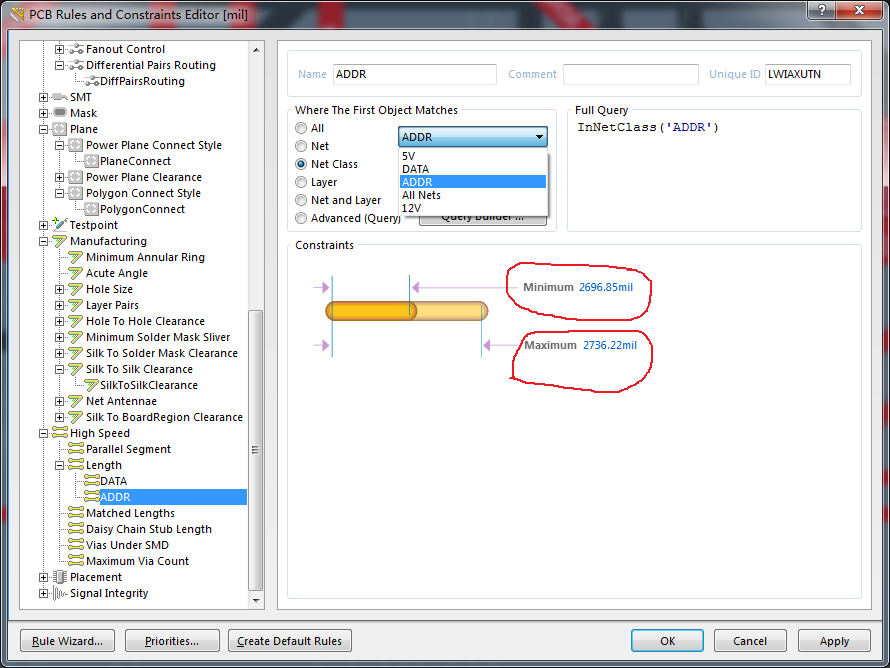

4、然后进入PCB,在PCB规则设置里面找到“Length”

添加一个“Length”规则,目标为刚刚的ADDR类,布线长度范围进行合适设置。如我们的目标长度是46.355mm,那么最小值就可以设为45.355mm,最大值设为46.356mm,整个类中网络的布线长度差1mm。(这个是按自己线路速度来定的,网上有公式可以大致计算)

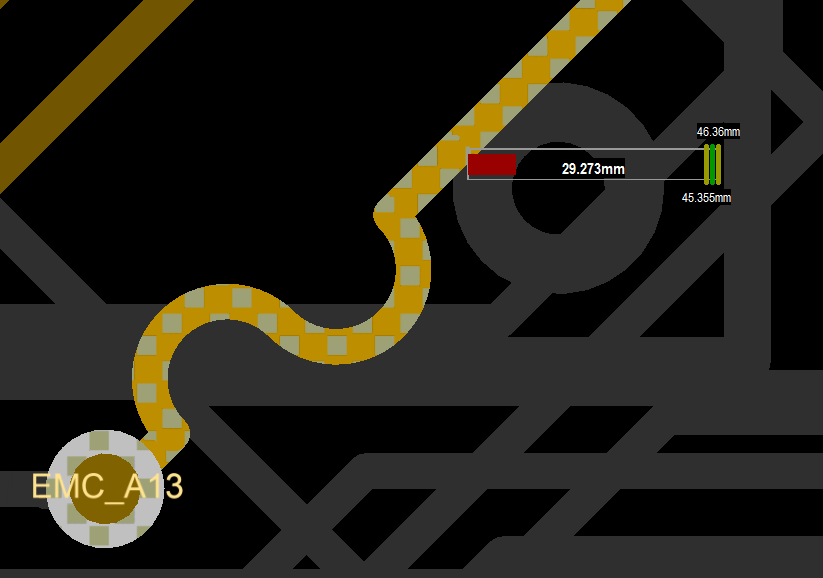

5、在PCB中,按“T”+“R”,鼠标变十字,点击要进行蛇形调整的对象,然后进行移动,目标布线就会自动变成蛇形线了。

同时会出现右边的尺标,提示目标布线长度范围和当前的布线长度。

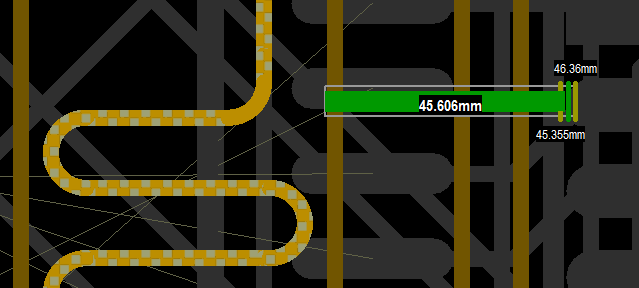

当布线长度满足目标要求时,尺标会变绿。

蛇形线的属性可以在布线状态下按“Tab”键唤出。

当然还可以用快捷键:

快捷键“,”“。”调整幅度。

“1”“2”调整蛇形线的拐角与弧度。

“3”“4”调整蛇形线的宽度。