对输出数据信号完整性和时钟信号电磁干扰(EMI)的比较

隔离的Σ-Δ调制器长期以来被证明可以在嘈杂的工业电机应用环境中提供非常高的精度和强劲的电流和电压感测能力。有两类隔离型Σ-Δ调制器:一种是在IC内部产生时钟信号;另一种是从外部时钟源接收时钟信号。 Σ-Δ调制器生成对应于输入模拟信号的输出数字比特流数据。输出数字数据必须尽可能与时钟信号同步。然后,微控制器以相同的时钟信号频率对该输出数据进行采样,以进一步滤波和抽取。

在本文中,将详细研究这两类隔离Σ-Δ调制器的输出数据信号完整性。并通过简单的电磁干扰(EMI)测试设置、对由这两类Σ-Δ调制器的高频时钟信号产生的EMI进行比较。

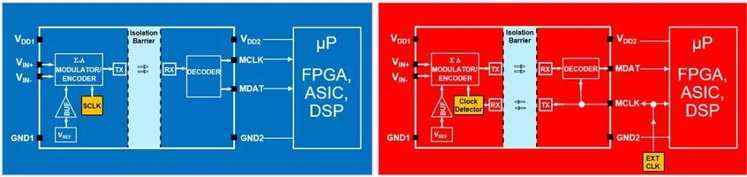

隔离型Σ-Δ调制器的简化框图

图1左侧的简化框图说明了典型的内(部)时钟隔离Σ-Δ调制器;右侧是典型的外(部)时钟隔离Σ-Δ调制器。对于内时钟型来说,抖动极低的时钟源构建在与Σ-Δ编码器相同的芯片上。重新生成输出MCLK,以允许输出数据位流MDAT被脉送进微控制器以进行抽取和滤波。对于外时钟型来说,外时钟源为Σ-Δ调制器和微控制器提供时钟信号。将在隔离栅的另一侧检测时钟信号。检测器必须能够承受一定程度的时钟抖动,并重构时钟信号,以实现Σ-Δ编码器的正常功能。

图1:左图是内时钟隔离的Σ-Δ调制器简化框图;右图是外时钟隔离的Σ-Δ调制器的简化框图;两者都连至微控制器。

输出数据信号完整性

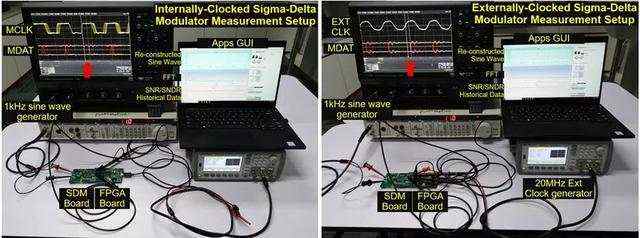

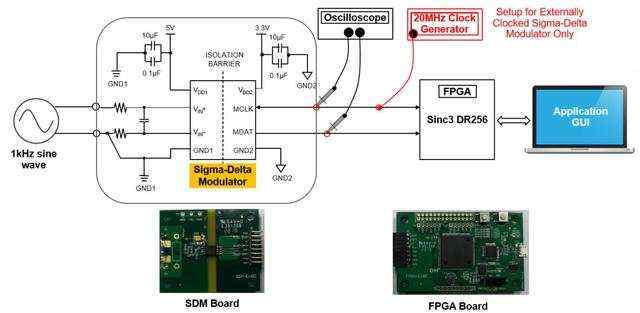

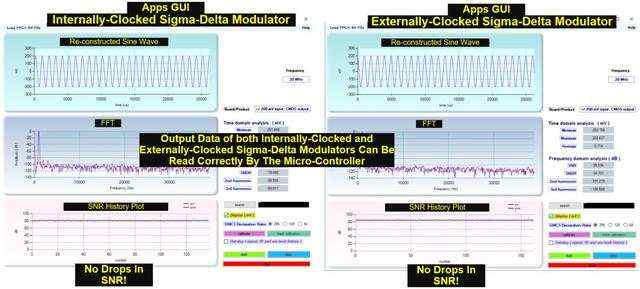

使用相同的微控制器(此例是FPGA),分别测量内和外时钟Σ-Δ调制器的信噪比(SNR)。这两类Σ-Δ调制器的测量设置是相同的,只是外时钟Σ-Δ调制器需要一个20MHz的外时钟源提供时钟信号。下面的图2a和2b显示了测量设置。将1kHz正弦波模拟电压信号注入Σ-Δ调制器的输入端,然后在FPGA处对相应的数字输出比特流数据进行采样,并经过称为抽取的滤波过程。笔记本电脑上显示的应用图形用户界面(GUI)显示了重构的正弦波、快速傅里叶变换(FFT),FFT用以计算信噪比(SNR)和SNR历史图与时间的对应关系。如果FPGA未能正确采样Σ-Δ输出数据比特流,则将清楚地观察到历史图上SNR的突然下降。

图2a:显示了具有相同FPGA板和应用软件的内和外时钟Σ-Δ调制器的测量设置。

图2b:显示了测量设置的简化示意图

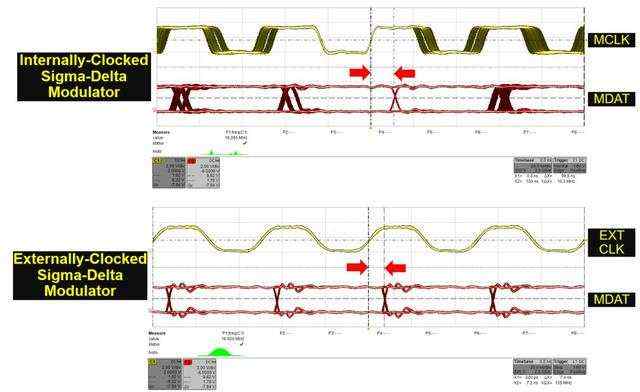

查看图3中示波器捕获的图像,内时钟Σ-Δ调制器的输出MCLK信号似乎是抖动的。但从输出时钟MCLK的上升沿到输出数据MDAT的上升沿或下降沿的时间延迟,对每个时钟周期看来都是相同的。同样,从外时钟到其输出MDAT的时间延迟似乎也是稳定的。这里可得出结论:对这两类Σ-Δ调制器,MDAT在每个时钟周期始终与MCLK同步。

图3:显示了示波器捕获的两类Σ-Δ调制器的MCLK和MDAT图像

从图4中所示的SNR历史图与时间的对比来看,对于两类Σ-Δ调制器都没有观察到SNR的突然下降。换句话说,FPGA(微控制器)可正确读取这两类Σ-Δ调制器的输出数据(MDAT)。

.图4:显示了应用GUI软件中的测量结果

高频时钟信号产生的EMI

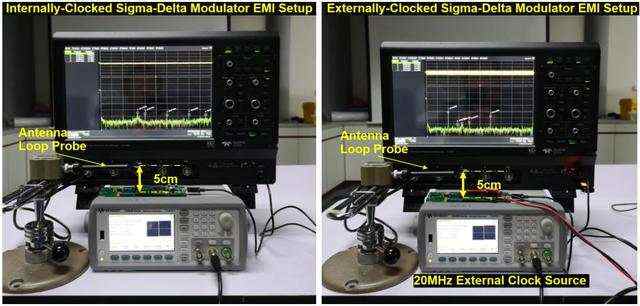

高频时钟信号是系统PCB板上EMI的主要来源之一。时钟频率越高、PCB走线越长,时钟信号产生的EMI就越严重。内时钟Σ-Δ调制器的时钟信号走线可以更短。一些内时钟的Σ-Δ调制器还结合了扩频技术来扩展时钟信号的频率峰值,以有效降低EMI。为证明这点,设置了一种如图5所示的简单EMI测量方法,以分别测量内和外时钟Σ-Δ调制器的时钟信号产生的EMI。将环形天线放置在Σ-Δ调制器评估板上方5cm处。示波器设置为将频率从0Hz扫频到100MHz。

图5:显示了该简单的EMI测量设置,用于测量两类Σ-Δ调制器的时钟信号的EMI

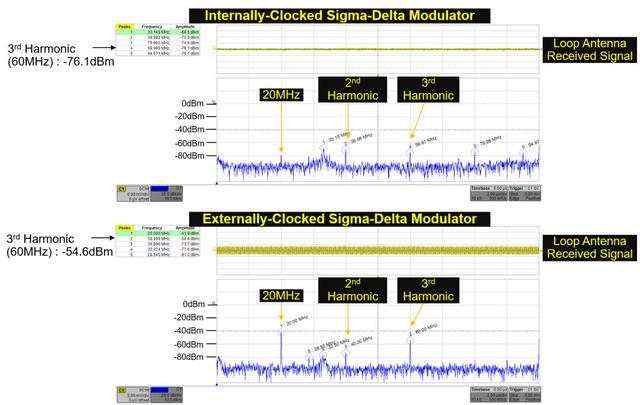

从图6中示波器捕获的图像可以清楚看出,外时钟源产生的EMI要高得多,在时钟信号频率及其谐波处达到峰值。例如,对于60MHz的三次谐波,外时钟源产生的EMI比内时钟Σ-Δ调制器输出时钟信号的高20dB。

图6:显示了进入外时钟Σ-Δ调制器的时钟信号产生的EMI要高得多,在时钟信号频率及其谐波处达到峰值

-END-

感谢您的阅读 请点击右下角“好看”