作者:博客百度2 | 来源:互联网 | 2023-10-13 12:24

8886的两种工作模式的配置一.最小与最大的工作模式最小工作模式MNMX*1(高电平)构成小规模的单处理机系统(只有个微处理器80888086)由CPU本身提供控制总线最大工作模式

88/86的两种工作模式的配置

一. 最小与最大的工作模式

最小工作模式

- MN/MX* = 1 (高电平)

- 构成小规模的单处理机系统 (只有个微处理器 8088/8086)

- 由CPU本身提供控制总线

最大工作模式

- MN/MX* = 0 (低电平)/地

- 构成大规模的多机系统

- 协处理器 8087(浮点运算)和 (I/0处理器)8089

- 8088和8288(总线控制器)共同形成系统总线信号

二. 8088最小模式与最大模式的总线形成

8088最小规模的系统总线形成

-

20位地址总线的形成

采用3片 8282进行锁存和驱动

(Inter 8282是三态透明地址缓冲器 8283

通用的集成电路芯片 74LS373 74LS273)

-

8位的数据总线的形成

数据收发器 8286 进行双向驱动

Inter 8286是双向三态8位缓冲器

Inter 8287

通用数字集成电路 74LS245等 都是双向

单向 接口电路中经常使用三态单向缓冲器 74LS244可以用 地址或者数据

-

系统控制信号的形成

由88/86 引脚直接提供

最大模式下的系统形成

- 地址总线:采用74LS373 和 74LS244

- 数据总线:采用74LS245形成和驱动

- 控制总线: 由系统总线控制器8288形成 MEMR* MEMW* IOR* IOW* INTA*

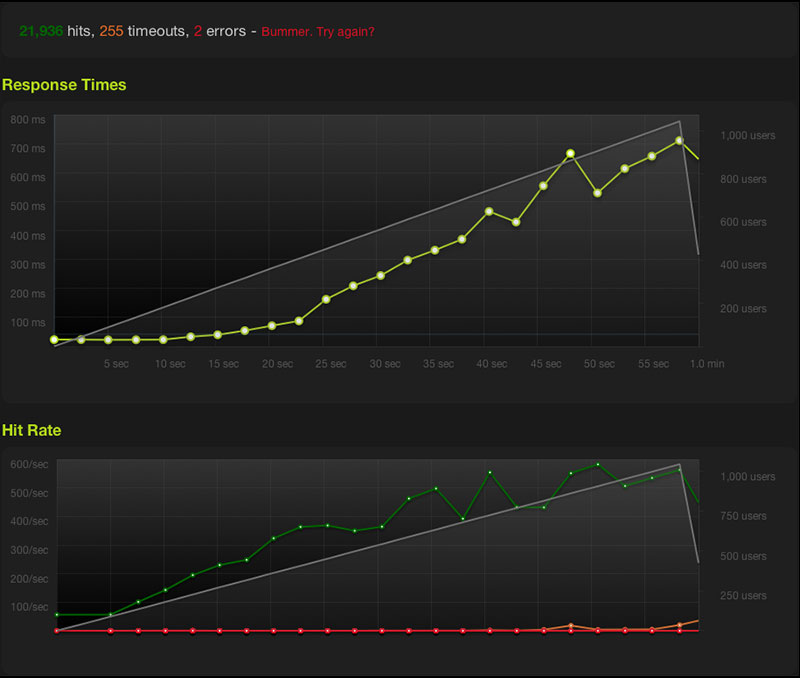

时序图

指令周期

- 一条指令从取指令到执行结束的时间

- 指令周期包括多个总线周期

- NMI INTR:cpu响应中断条件 指令周期结束

总线周期

88/86 最基本的总线周期需要四个时钟周期

若READY在T3测试时为0 则T3~T4之间插入 Tw

时钟周期

T1 若CPU主频=5MHZ , T1=200ns

构成总线周期 => 指令周期

等待状态

通过插入Tw 使速度差别较大的两个部件 保持同步

在读写总线周期中 判断是否插入 Tw

- T3的前沿检测 READY 引脚是否有效

- READY无效 =0 在 T3~T4之间 插入 一个 Tw 再检测

- READY 有效 进入 T4

启动与复位

88/86 CPU引脚 RESET引脚用来使CPU复位/启动

8086服务后 PSW ,DS , ES ,SS和其他寄存器清零 指令队列也清零

段寄存器 CS 初始化位 FFFFH 指令指针IP 初始化位 0000H

中断系统

中断响应周期

CPU在每条指令的T4 检测 INTR* 信号 若有效 IF=1 开中断 则 CPU在当前指令执行完毕以后乡音 进入中断响应周期

中断

当Cpu在执行主程序时 外/内原因 暂时中断主程序的运行 转而去执行子程序,当子程序结束后返回主程序过程

中断源

引起中断的原因或事件 包括外设出现故障和CPU内部执行时出现的异常

中断类型

(外中断和内中断) 88/86系统能处理256个中断

中断类型号

用0-255 (00H-FFH)给256个中断分配编号

在INTA*的响应 第二个周期 由 8259向CPU通道D0~D7传递中断类型号n

CPU获取中断类型号的方式

INTR的中断号由8259中断控制器提供

指令中断(INT n) 的中断号由指令直接给出

NMI 其他中断 由系统预设

中断向量

中断服务子程序 的入口地址 有逻辑地址 CS:IP表示 (段地址:偏移地址) 32位 4字节

中断向量表

存放中断向量的内存空间

256个中断向量 每个向量占用4个字节 共占用 1KB

每个中断向量的低字表示偏移地址 每个高字表示段地址 需占用4个字节

物理地址 00000H-003FFH 地址依次安排各个中断向量 向量从0开始

向量号为n的中断向量的物理地址 = n*4

容量: = 末地址+1-首地址

3FF+1 -0

400= 22*(24)2=210

中断类型

外部的中断 17# NMI 和 18# INTR

非屏蔽中断和可屏蔽中断的特点

| 非屏蔽中断 NMI | 可屏蔽中断 INTR |

|---|

| 通过NMI向CPU提出中断请求 | 外设通过INTR向CPU提出中断请求 |

| CPU无法禁止 (非屏蔽) | 在允许中断 当前指令结束后 予以响应输出INTA* |

| 在当前指令执行结束后予以响应 | IF=1 开中断 允许响应 IF=0 关中断 禁止中断 |

| 中断向量号为2 | 向量号有8259(中断控制器)提供 |

| 主要用于处理系统意外和故障 | 主要用于主机与外设交换数据 |

IF的状态 (中断标志)

| IF=0 可屏蔽中断不会被响应 | IF=1 可屏蔽中断会被响应 |

|---|

| 关中断 屏蔽中断 中断屏蔽 | 开中断 允许中断 中断开放 |

| 系统复位 使 IF=0 | |

| 中断被响应 使 IF=0 | |

| 执行指令 CLI 使IF=0 | 执行指令 IRET 恢复原IF状态 |

优先级(中断)

软件中断 优 ↓

除法错中断 0

指令中断 n

断点中断 3

溢出中断 4

非屏蔽中断 2

可屏蔽中断 n外

单步中断 1

中断过程

五个步骤

中断请求→中断优先级判定→中断响应→中断处理(服务)→中断返回

中断响应过程

Cpu在每执行完一条指令后 如果允许CPU响应 则CPU自动完成以下工作

-

取中断类型号 n

-

标志寄存器入栈 (PSW入栈)

-

IF=TF=0

-

CS和IP入栈

-

获取中断向量号(CS:IP)

执行两个总线读周期 在中断向量表中 n*4 开始的单元取两个字 分别送到IP和CS 获取中断向量处理程序入口地址

CPU从新CS:IP)值开始执行中断处理程序

中断服务程序的一般构成

开中断 STI

保护现场 Push

中断服务

关中断 CTI

恢复现场 Pop

中断返回 IRET